# CAPACITOR VOLTAGE BALANCING, FAULT DETECTION, AND FAULT TOLERANT CONTROL TECHNIQUES OF MODULAR MULTI-LEVEL CONVERTERS

A thesis submitted in partial fulfilment of the requirement of Staffordshire University for the degree of Doctor of Philosophy

August 2016

#### **Abstract**

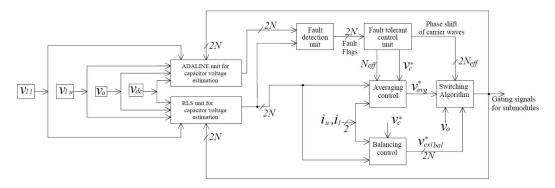

Modular Multilevel Converters (MMCs) are distinguished by their modular nature that makes them suitable for wide range of high power and high voltage applications. However, they are vulnerable to internal faults because of the large number of series connected Sub-Modules. Additionally, it is highly recommended not to block the converter even if it is subjected to internal faults to secure the supply, to increase the reliability of the system and prevent unscheduled maintenance. This thesis introduces a fault tolerant control system for controlling the MMC in normal as well as abnormal operating conditions. This is done through developing a new adaptive voltage balancing strategy based on capacitor voltage estimation utilizing ADAptive Linear NEuron (ADALINE) and Recursive Least Squares (RLS) algorithms. The capacitor voltage balancing techniques that have been proposed in literature are based on measuring the capacitor voltage of each sub-module. On contrary, the proposed strategy eliminates the need of these measurements and associated communication links with the central controller.

Furthermore, the thesis presents a novel fault diagnosis algorithm using the estimated capacitor voltages which are utilized to detect and localize different types of sub-module faults. The proposed fault diagnosis algorithm surpasses the methods presented in literature by its fast fault detection capability without the need of any extra sensing elements or special power circuit.

Finally, a new Fault Tolerant Control Unit (FTCU) is proposed to tolerate the faults located inside the MMC submodules. The proposed FTCU is based on a sorting algorithm which modifies the parameters of the voltage balancing technique in an adaptive manner to overcome the reduction of the active submodules and secure the MMC operation without the need of full shut-down. Most of fault tolerant strategies that have been proposed by other researchers are based on using redundant components, while the proposed FTCU does not need any extra components.

The dynamic performance of the proposed strategy is investigated, using PSCAD/EMTDC simulations and hardware in the loop (HIL) real-time simulations, under different normal and faulty operating conditions. The accuracy and the time response of the proposed fault detection and tolerant control units result in stabilizing

the operation of the MMC under different types of faults. Consequently, the proposed integrated control strategy improves the reliability of the MMC.

#### **Acknowledgments**

First and above all, I praise God, the almighty for providing me this opportunity and granting me the capability to proceed successfully. This thesis appears in its current form due to the assistance and guidance of several people. I would therefore like to offer my sincere thanks to all of them.

Prof. Sarath Tennakon, my esteemed principal supervisor, my cordial thanks for accepting me as a PhD student, your warm encouragement, thoughtful guidance, critical comments, and correction of the thesis.

I want to express my deep thanks to my esteemed external supervisor Dr Mostafa Marei for the trust, the insightful discussion, offering valuable advice, for your support during the whole period of the study, and especially for your patience and guidance during the writing process.

I would like to thank my esteemed second supervisor, Dr Alison Griffiths for her excellent advises throughout the PhD period.

Hatem Diab, I greatly appreciate your excellent assistance and your spiritual supports for me during my PhD study. I will never forget the hard times that would never have been passed without you standing to me. Your situations have always showed a real man and best friend who always exerts the maximum effort to support others, really thank you very much.

Many thanks to the management of Staffordshire University for allowing me to use the university' facilities and helping me in getting anything I need during my study.

Thanks also to all of my research colleagues, Hesham, Hussain, Samir, Mahmoud, Raouf, Monday, Masoom, Ernest and Masoud for providing a good atmosphere in our department and for useful discussions.

I would like to express my greatest gratitude to Prof. Yasser Galal for his endless support and sharp actions that helped me to take the opportunity of studying abroad.

I also appreciate the financial support of the Arab Academy for Science and Technology and Maritime Transport, during my PhD study.

I cannot finish without thanking my Father who passed away during my study, although you are not with me but I live with your advices and encouragements through our life.

I warmly thank and appreciate my mother for her spiritual support in all aspects of my life. Although I have lived far from you, but communication with you, provided emotional atmosphere for me.

I also would like to thank my sisters, Mai and Yomna, they have provided assistance in numerous ways. Also, I want to thank my father and mother in law for their support and help during this journey.

I want to express my gratitude and deepest appreciation to my lovely sweet daughter, Lilia. Your smile was one of the greatest sources of motivation to work, thanks for being in my life.

And finally, my lovely wife, Dear Amira, without your supports and encouragements, I could not have finished this work, it was you who kept the fundamental of our family, and I understand it was difficult for you, therefore, I can just say thanks for everything and may Allah give you all the best in return.

#### **Table of Contents**

| Abstract    |                                                                                                                          | I    |

|-------------|--------------------------------------------------------------------------------------------------------------------------|------|

| Acknowle    | dgments                                                                                                                  | II   |

| Table of C  | ontents                                                                                                                  | V    |

| List of Fig | ures                                                                                                                     | X    |

| List of Tal | oles                                                                                                                     | (VII |

| List of Ab  | breviationsX                                                                                                             | VIII |

|             |                                                                                                                          |      |

| -           | - Introduction                                                                                                           |      |

| 1.1         | Background                                                                                                               |      |

| 1.2         | Motivation and Research Objectives                                                                                       |      |

| 1.3         | Thesis Outline                                                                                                           |      |

| 1.4         | List of Publications                                                                                                     |      |

| 1.4.1       | Journal publications                                                                                                     |      |

| 1.4.2       | Conference publications                                                                                                  |      |

| 1.4.3       | Co-authored conference publications                                                                                      | 9    |

|             | 2 – Modular Multilevel Converters: Structure, Operation,                                                                 |      |

| 2.1         | Introduction                                                                                                             |      |

| 2.2         | Multilevel Converters                                                                                                    |      |

| 2.2.1       | Cascaded H-Bridge converter                                                                                              |      |

| 2.2.2       | Neutral-point clamped multilevel converters                                                                              | 12   |

| 2.2.3       | Flying capacitor multilevel converters                                                                                   |      |

| 2.2.4       | Hybrid multilevel converters                                                                                             |      |

| 2.3         | Modular Multilevel Converters                                                                                            | 15   |

| 2.3.1       | MMC modes of operation                                                                                                   | 16   |

| 2.3.2       | MMC mathematical model                                                                                                   | 17   |

| 2.4         | Modulation Techniques of the MMC                                                                                         | 19   |

| 2.4.1       | Space vector modulation                                                                                                  | 19   |

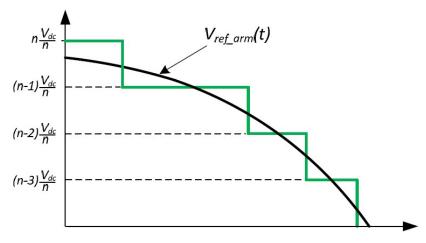

| 2.4.2       | Nearest level modulation                                                                                                 | 20   |

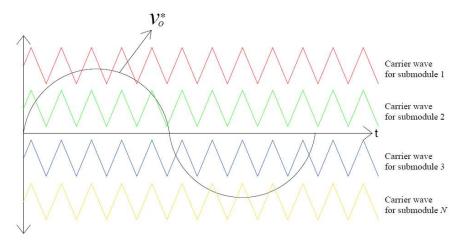

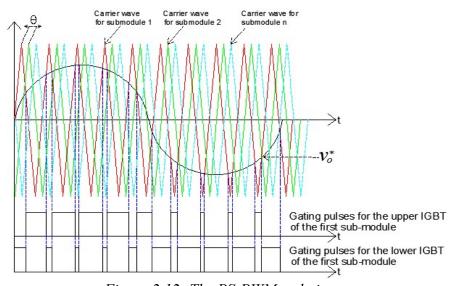

| 2.4.3       | Carrier-based pulse-width modulation                                                                                     | 22   |

| 2.5         | Design Considerations of MMCs                                                                                            | 24   |

| 2.5.1       | Submodule capacitance                                                                                                    |      |

| 2.5.2       | Arm inductance                                                                                                           |      |

| 2.6         | Chapter Summary                                                                                                          | 26   |

| -           | – Review of Capacitor Voltage Balancing, Fault Detection, and F<br>Control Techniques of Modular Multilelevel Converters | ault |

| 3.1              | Introduction                                                                              | .27 |

|------------------|-------------------------------------------------------------------------------------------|-----|

| 3.2              | Capacitor Voltage Balancing of MMC Submodules                                             | .27 |

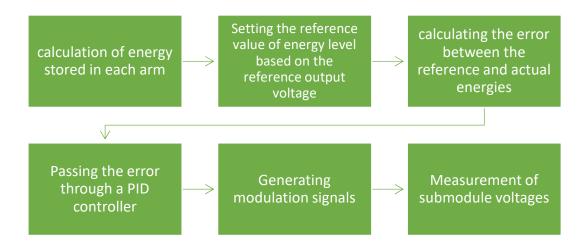

| 3.2.1            | Capacitor voltage balancing based on energy control                                       | .28 |

| 3.2.2            | Capacitor voltage balancing based on distributed control                                  | .29 |

| 3.2.3 modulation | Capacitor voltage balancing based on reduced switching frequents                          | -   |

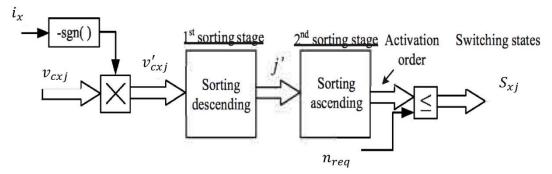

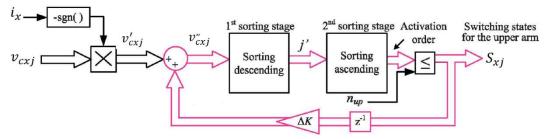

| 3.2.4            | Capacitor voltage balancing based on sorting algorithms                                   | .31 |

| 3.3              | The MMC Submodule Faults                                                                  | .33 |

| 3.3.1            | Faults in power electronic devices                                                        | .34 |

| 3.3.2            | Faults in submodule capacitors                                                            | .36 |

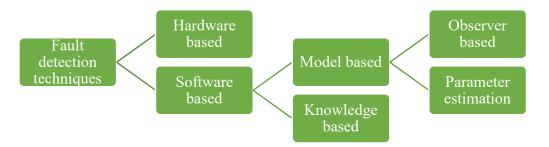

| 3.4              | The Concept of Fault Detection                                                            | .36 |

| 3.4.1            | Hardware-based fault detection                                                            | .37 |

| 3.4.2            | Software-based fault detection                                                            | .37 |

| 3.5              | Fault Detection Techniques in MMCs                                                        | .38 |

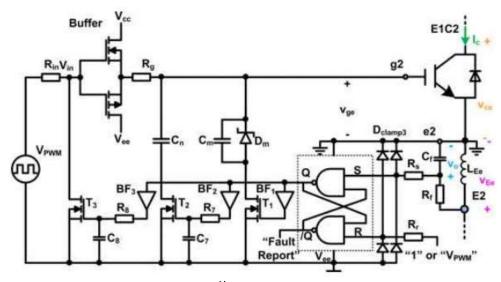

| 3.5.1            | IGBT fault detection using the rate of change of the collector current                    | 39  |

| 3.5.2            | IGBT fault detection using the behaviour of the gate voltage                              | .39 |

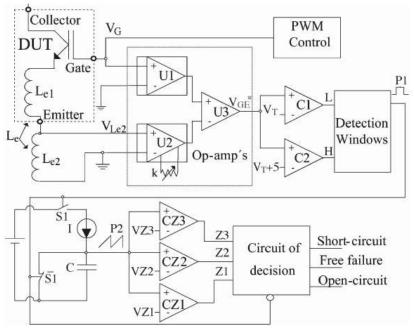

| 3.5.3 voltage    | Submodule fault detection using the measurements of submodule out                         |     |

| 3.5.4            | IGBT fault detection using artificial neural networks                                     | .42 |

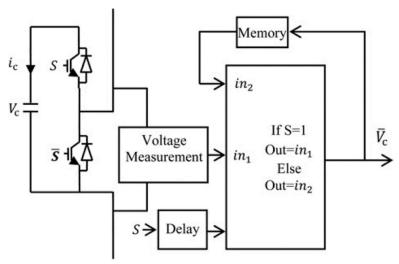

| 3.5.5            | Submodule fault detection using sliding mode observation                                  | .43 |

| 3.6              | The Concept of Fault Tolerant Control                                                     | .45 |

| 3.6.1            | Active fault tolerant control                                                             | .45 |

| 3.6.2            | Passive fault tolerant control                                                            | .46 |

| 3.7              | Fault Tolerant Control of MMCs                                                            | .46 |

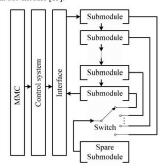

| 3.7.1            | Fault tolerant control using redundant submodules                                         | .47 |

| 3.7.2            | Fault tolerant control using redundant IGBTs                                              | .48 |

| 3.8              | Chapter Summary                                                                           | .49 |

| -                | 4 – Proposed Capacitor Voltage Balancing Technique Based<br>Voltage Estimation Algorithms |     |

| 4.1              | Introduction                                                                              | .51 |

| 4.2              | Proposed Technique of Capacitor Voltage Balancing                                         | .52 |

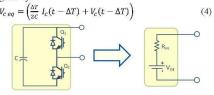

| 4.2.1            | The capacitor voltage estimation technique                                                | .52 |

| 4.2.1.1          | Capacitor voltage estimation using ADALINE technique                                      | .53 |

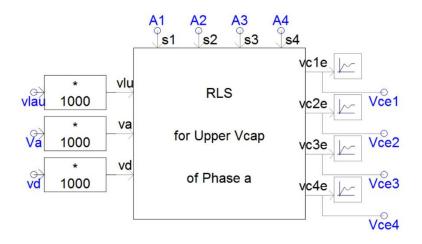

| 4.2.1.2          | The capacitor voltage estimation using RLS technique                                      | .55 |

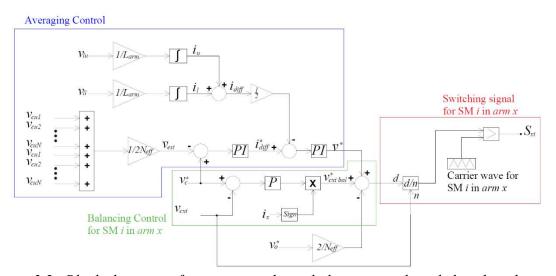

| 4.2.2            | The averaging control                                                                     | .58 |

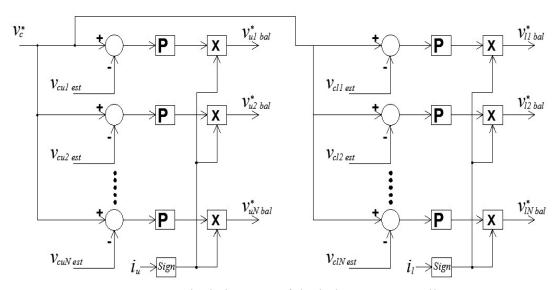

| 4.2.3            | Balancing control                                                                         | .61 |

| 4.3              | MMC Simulation Models                                                                     | .62 |

| 4.3.1            | MMC Model 1                                                                               | .63 |

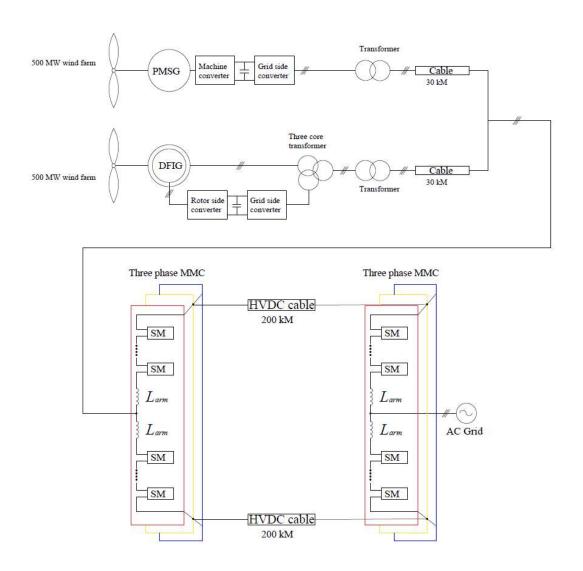

| 4.3.2             | MMC Model 264                                                                         |

|-------------------|---------------------------------------------------------------------------------------|

| 4.4               | Simulation Results                                                                    |

| 4.4.1 estimation  | Case 1: Dynamic performance of the proposed capacitor voltage -based control strategy |

| 4.4.2<br>MMC      | Case 2: Dynamic performance during the boosting operation of the                      |

| 4.4.3 connected   | Case 3: Performance of capacitor voltage estimation algorithm in grid-MMC             |

| 4.5               | Chapter Summary                                                                       |

| -                 | 5 – Proposed Fault Detection Technique Based on Capacitor Voltage<br>n Algorithms77   |

| 5.1               | Introduction                                                                          |

| 5.2               | The Proposed Fault Detection Strategy                                                 |

| 5.3               | Simulation Results                                                                    |

| 5.3.1             | Case 1: Performance under IGBT open circuit fault81                                   |

| 5.3.2             | Case 2: Performance under IGBT short circuit fault85                                  |

| 5.3.3             | Case 3: Performance under multiple faults in two different arms89                     |

| 5.4               | Chapter Summary93                                                                     |

| _                 | 6 – Proposed Fault Tolerant Control Strategy Based on a Sorting                       |

| 6.1               | Introduction94                                                                        |

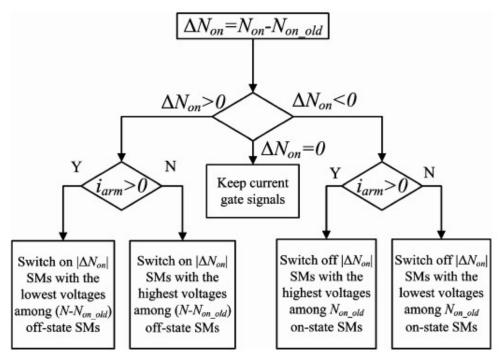

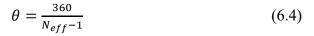

| 6.2               | The Proposed Fault Tolerant Control Algorithm95                                       |

| 6.3<br>Technique  | Reliability Assessment of the Proposed Fault Tolerant Control                         |

| 6.3.1             | MMC reliability definitions                                                           |

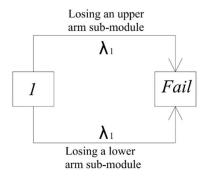

| 6.3.2             | Reliability calculations for MMC without fault tolerant control99                     |

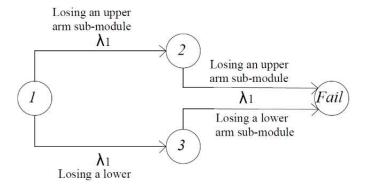

| 6.3.3 tolerant co | Reliability calculations for MMC with the redundancy based fault introl               |

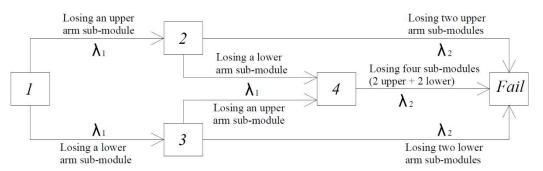

| 6.3.4             | Reliability calculations for MMC with the proposed fault tolerant control             |

| 6.4               | Simulation Results                                                                    |

| 6.4.1             | Case 1: The FTCU Performance under IGBT open circuit fault103                         |

| 6.4.2             | Case 2: The performance under IGBT short circuit fault                                |

| 6.4.3             | Case 3: The performance of the FTCU under multiple faults109                          |

| 6.4.4             | Case 4: The performance of the FTCU under cascading failures112                       |

| 6.5               | Chapter summary                                                                       |

|                   | 7 – Validaiton of Proposed Techniques Using Hardware in The Loop<br>e Simulations     |

| 7.1               | Introduction                                                                          |

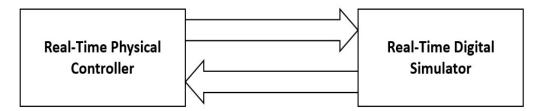

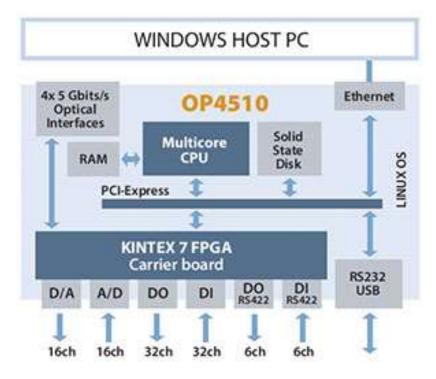

| 7.2                | HIL System Description                                                             | 118 |

|--------------------|------------------------------------------------------------------------------------|-----|

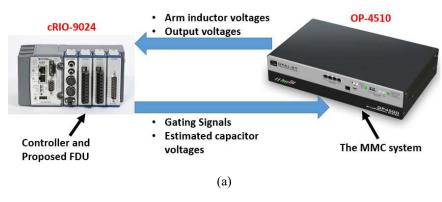

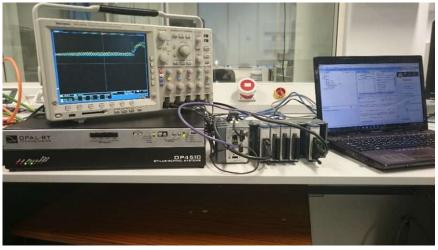

| 7.3                | HIL System Implementation                                                          | 119 |

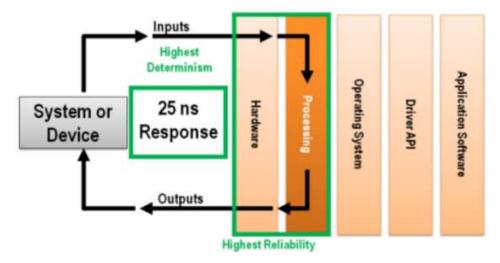

| 7.3.1              | The real-time physical controller                                                  | 120 |

| 7.3.2              | The real-time digital simulator                                                    | 121 |

| 7.4                | Practical Assessment of The Proposed Techniques                                    | 122 |

| 7.5                | HIL Simulation Results                                                             | 124 |

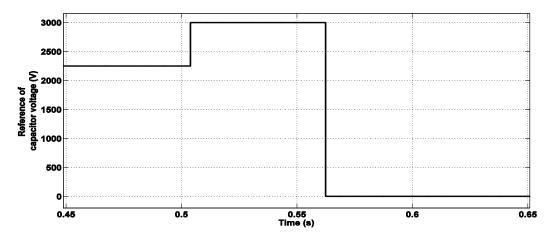

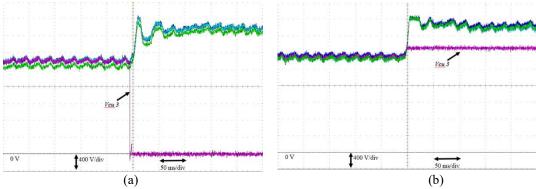

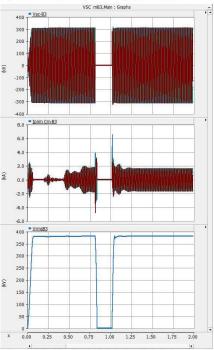

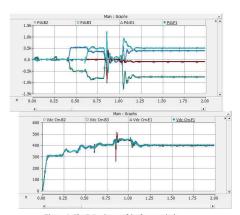

| 7.5.1 of output v  | Case 1: The performance of the proposed control under dynamic charoltage reference |     |

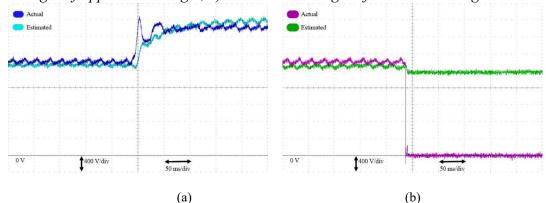

| 7.5.2 circuit faul | Case 2: The performance of the propsoed control under IGBT o                       | _   |

| 7.5.3 circuit faul | Case 3: The performance of the proposed control under IGBT slat                    |     |

| 7.5.4 submodule    | Case 4: The performance of the proposed control under multi-                       |     |

| 7.5.5 failures     | Case 5: The Performance of the propsoed control under cascade                      | _   |

| 7.6                | Chapter Summary                                                                    | 136 |

| Chapter 8          | - Conclusion                                                                       | 137 |

| 8.1                | Conclusion                                                                         | 137 |

| 8.2                | Summary of Contributions.                                                          | 138 |

| 8.3                | Further Research and expected outcomes                                             | 139 |

| Reference          | s                                                                                  | 140 |

| Appendix           | A – Modelling of Wind Energy Conversion Systems                                    | 152 |

| A.1 Model          | ling of the Wind Turbine                                                           | 152 |

| A.2 Model          | ling of PMSG                                                                       | 153 |

| A.3 Model          | ling of the DFIG                                                                   | 153 |

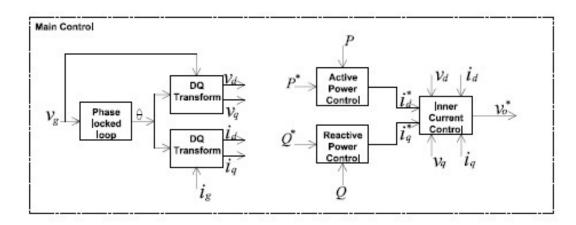

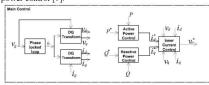

| A.4 Contro         | ol of Active and Reactive Power Injected into the Grid                             | 155 |

| A.4.1 Phas         | se locked loop                                                                     | 155 |

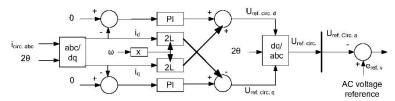

| A.4.2 AC a         | and DC voltage control loops                                                       | 155 |

| A.4.3 Inne         | r current loop                                                                     | 156 |

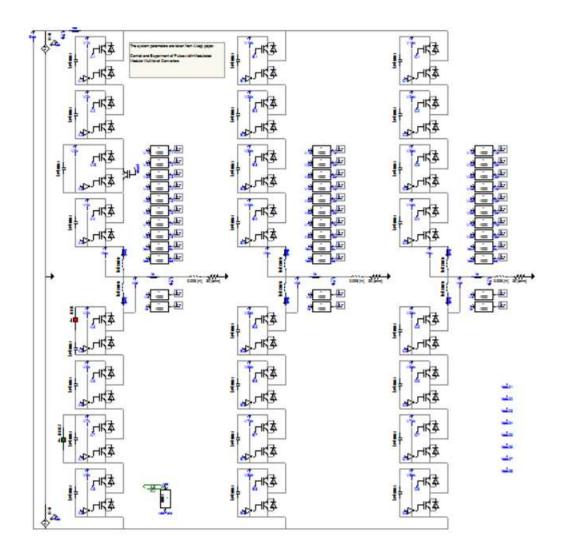

| Appendix           | B – Details of PSCAD Simulation Models                                             | 157 |

| Appendix           | C – Details of HIL Real-Time Simulations                                           | 170 |

| C.1 The R          | T-LAB/Simulink Real-time Simulation Model                                          | 171 |

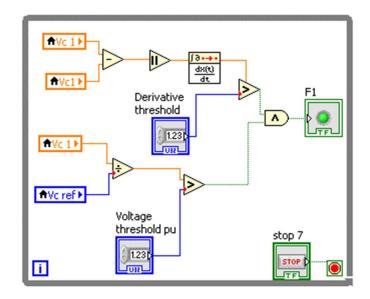

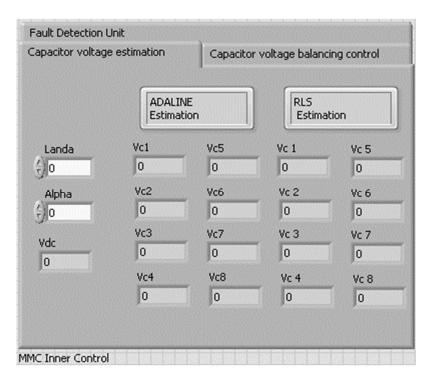

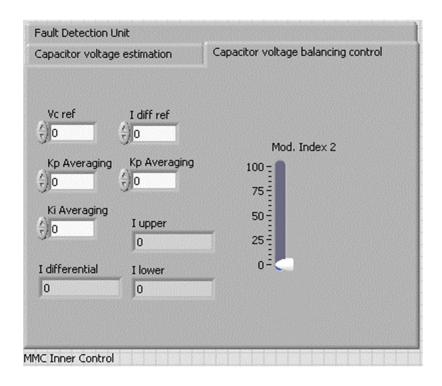

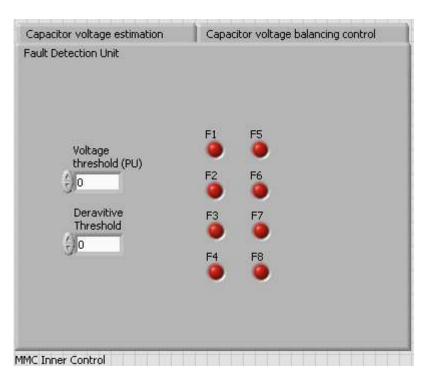

| C.2 The cF         | RIO/LABVIEW Programming Blocks                                                     | 179 |

| Appendix           | D – Selected Publications                                                          | 184 |

# **List of Figures**

| Figure 1.1: A 401-level MMC made by Siemens: a) a picture of the MMC, b) a                                  |

|-------------------------------------------------------------------------------------------------------------|

| picture for the submodule                                                                                   |

| Figure 1.3: Faults probabilities in power converters                                                        |

| Figure 2.1: Types of multilevel converters                                                                  |

|                                                                                                             |

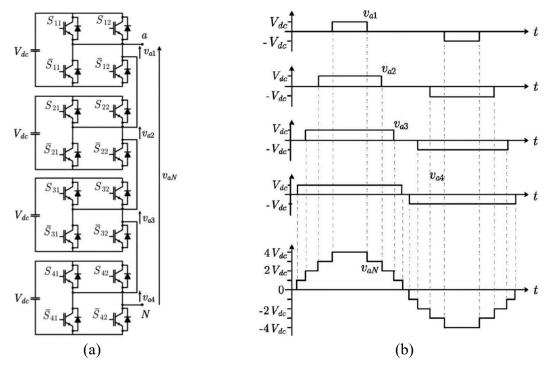

| Figure 2.2: Cascaded H-Bridge converter: a) the structure, b) the waveform of output voltage                |

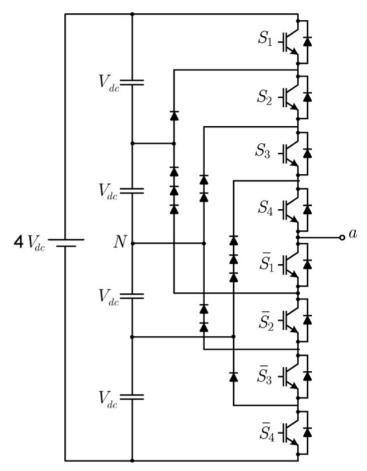

| Figure 2.3: Structure of neutral-point clamped multilevel converter                                         |

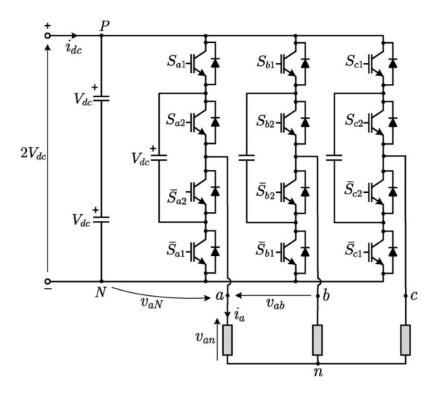

| Figure 2.4: The structure of flying capacitor multilevel converters                                         |

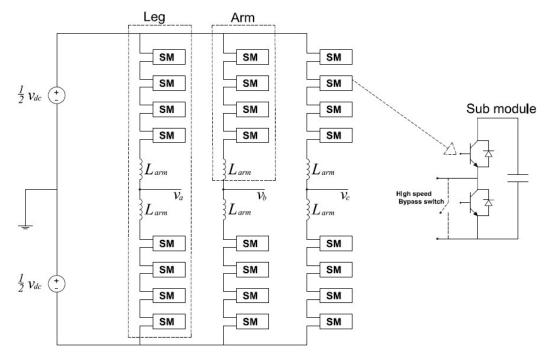

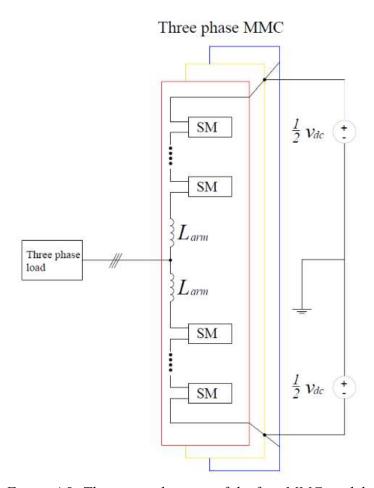

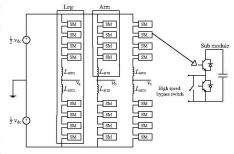

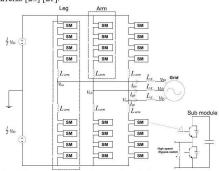

| Figure 2.5: Three-phase MMC topology and internal submodule                                                 |

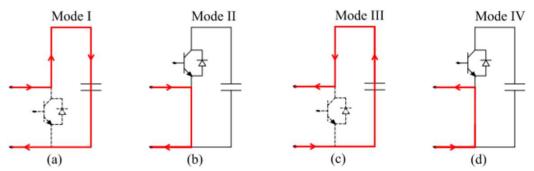

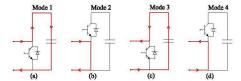

| Figure.2.6: Different operating modes of MMC submodules                                                     |

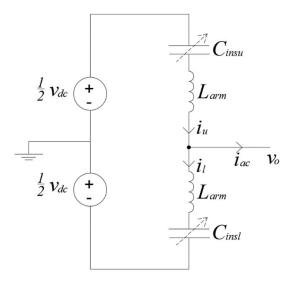

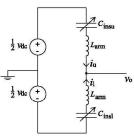

| Figure 2.7: MMC average circuit diagram                                                                     |

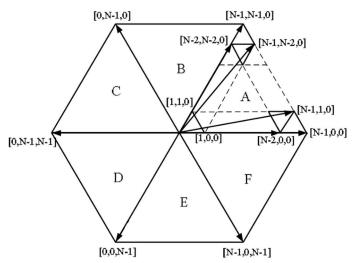

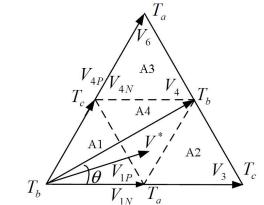

| Figure 2.8: Switching plan of space vector for an N level MMC20                                             |

| Figure 2.9: The triangle of stationary vectors                                                              |

| Figure 2.10: The NLM technique.                                                                             |

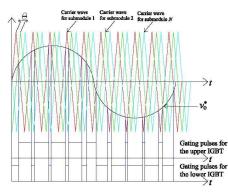

| Figure 2.11: The LS-PWM technique23                                                                         |

| Figure 2.12: The PS-PWM technique                                                                           |

| Figure 3.1: Block diagram of capacitor voltage balancing based on energy control                            |

| Figure 3.2: Block diagram of capacitor voltage balancing based on distributed control                       |

| Figure 3.3: Block diagram of capacitor voltage balancing based on reduced switching frequency modulation    |

| Figure 3.4: Block diagram of the conventional sorting algorithm based capacitor voltage balancing algorithm |

| Figure 3.5: Block diagram of the modified sorting algorithm based capacitor voltage balancing algorithm     |

| Figure 3.6: Types of fault detection techniques                                                             |

| Figure 3.7: The $\frac{di_c}{dt}$ measuring circuit                                                         |

| Figure 3.8: Gate voltage-based fault detection circuit                                                      |

| Figure 3.9: Block diagram of the submodule output voltage and derivation of capacitor voltage               |

| Figure 3.10: Flowchart of submodule output voltage-based fault detection41                                  |

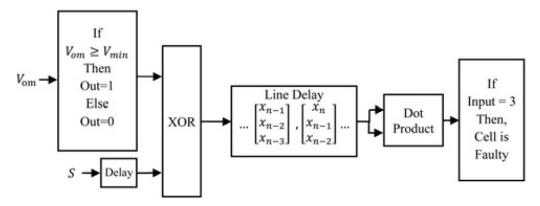

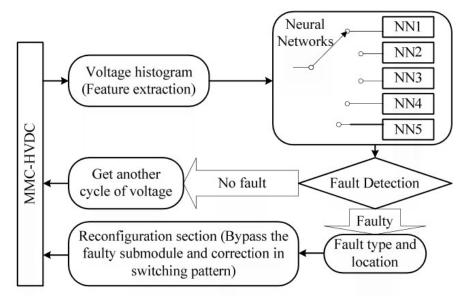

| Figure 3.11: The block diagram of the ANN IGBT fault detection method43                                     |

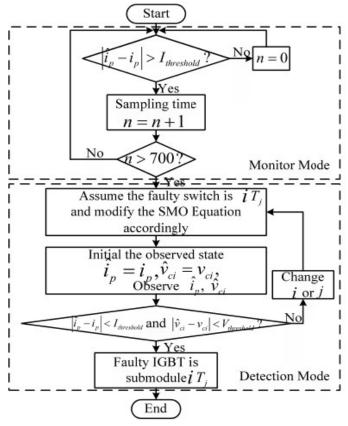

| Figure 3.12: Flowchart of the SMO submodule fault detection technique43                                     |

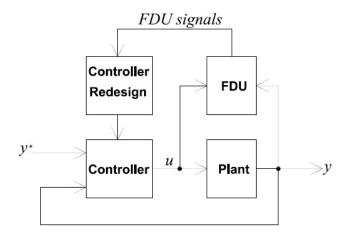

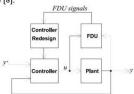

| Figure 3.13: Structure of active FTC                                                                        |

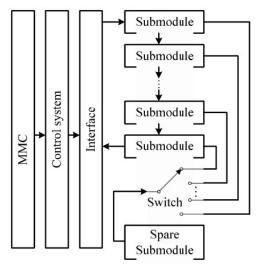

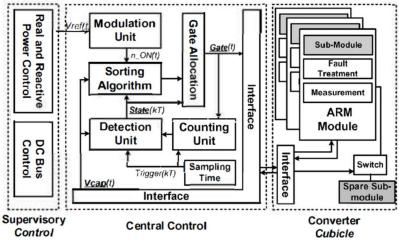

| Figure 3.14: Structure of MMC with redundant submodules                                                     |

| Figure 3.15: Block diagram of fault tolerant control with redundant submodules                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

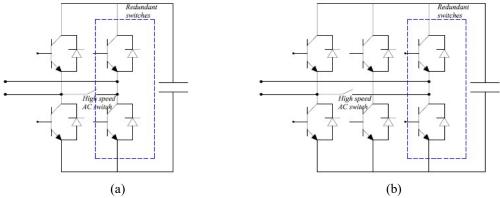

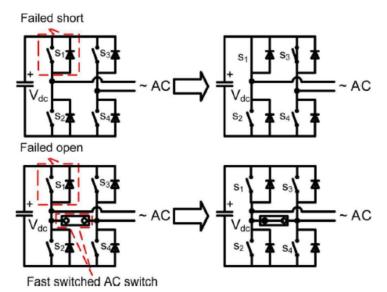

| Figure 3.16: The diagram of MMC submodule with IGBT redundanct for: a) half bridge, b) full bridge                                                                                                                                                                       |

| Figure 3.17: Tolerating the faults using redundant IGBTs                                                                                                                                                                                                                 |

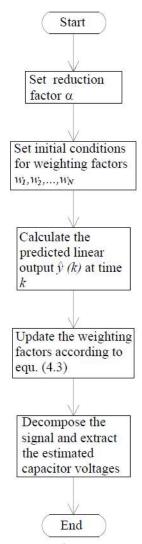

| Figure 4.1: Flow chart of capacitor voltage estimation using ADALINE technique                                                                                                                                                                                           |

| Figure 4.2: Flow chart of capacitor voltage estimation using RLS technique56                                                                                                                                                                                             |

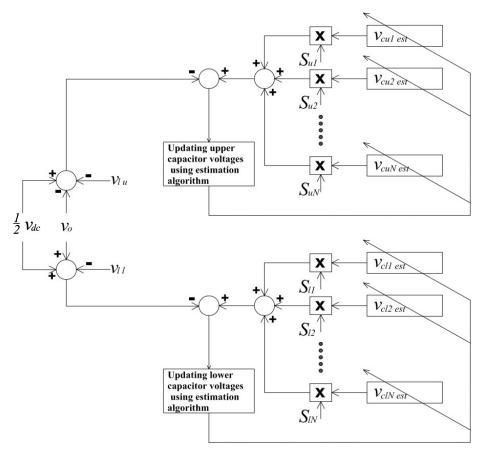

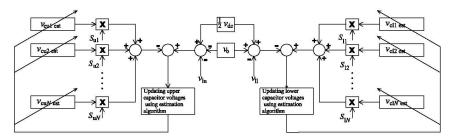

| Figure 4.3: Block diagram of capacitor voltage estimation unit                                                                                                                                                                                                           |

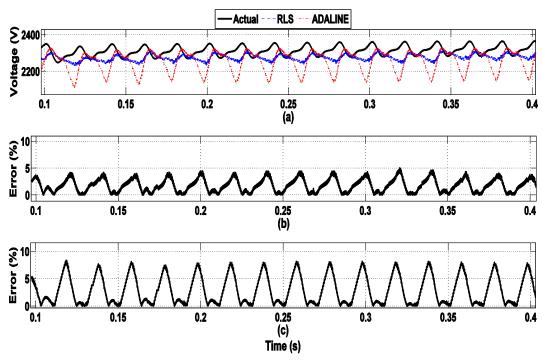

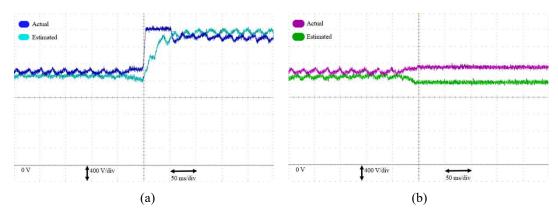

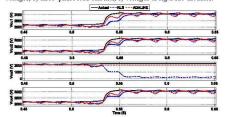

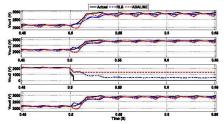

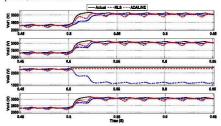

| Figure 4.4: Comparison between the RLS and ADALINE performances: a) actual capacitor voltages versus RLS and ADALINE estimated signals, b) percentage error between actual voltage and RLS estimation, c) percentage error between actual voltage and ADALINE estimation |

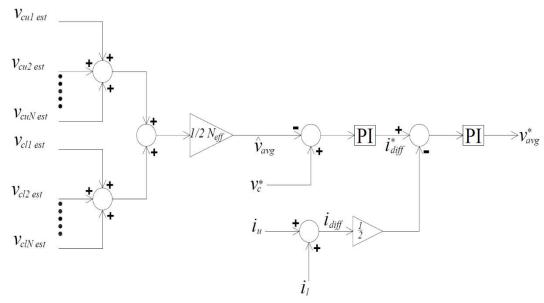

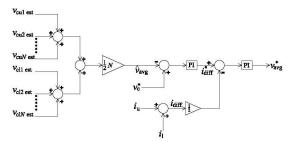

| Figure 4.5: Block diagram of the averaging controller                                                                                                                                                                                                                    |

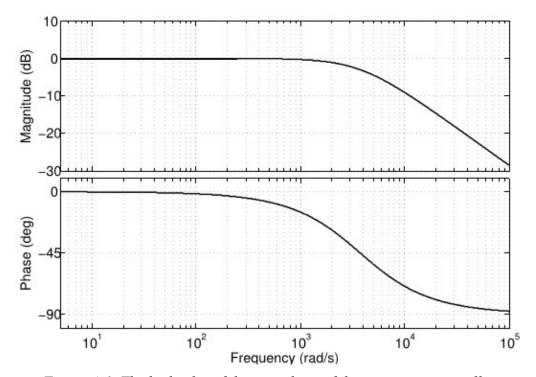

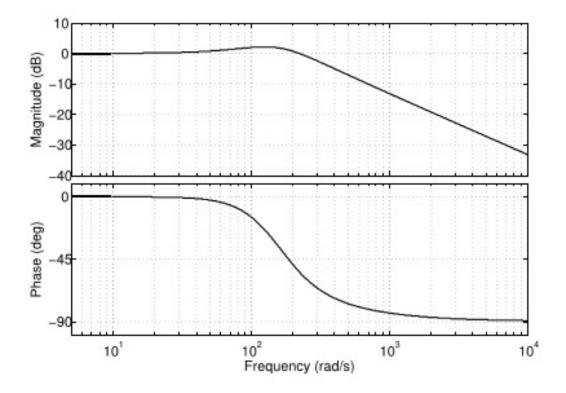

| Figure 4.6: The bode plot of the inner loop of the averaging controller60                                                                                                                                                                                                |

| Figure 4.7: The bode plot of the outer loop of the averaging controller61                                                                                                                                                                                                |

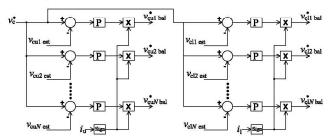

| Figure 4.8: Block diagram of the balancing controller                                                                                                                                                                                                                    |

| Figure 4.9: The circuit diagram of the first MMC model                                                                                                                                                                                                                   |

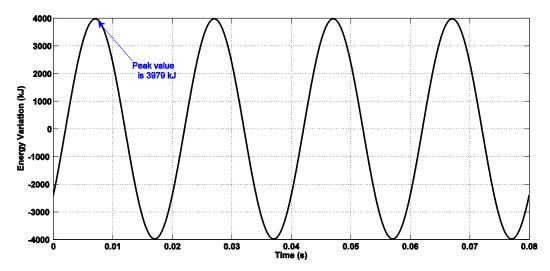

| Figure 4.10: The arm energy variation of the MMC simulated in the first model64                                                                                                                                                                                          |

| Figure 4.11: The circuit diagram of the second MMC model65                                                                                                                                                                                                               |

| Figure 4.12: The arm energy variation of the MMC simulated in the second model                                                                                                                                                                                           |

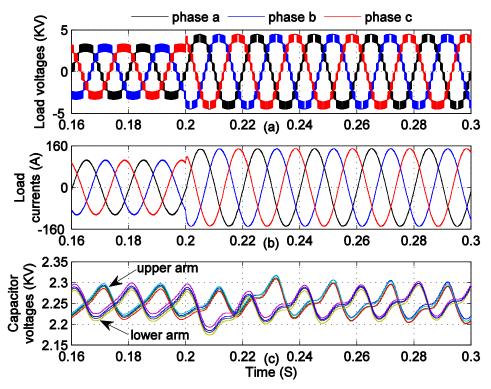

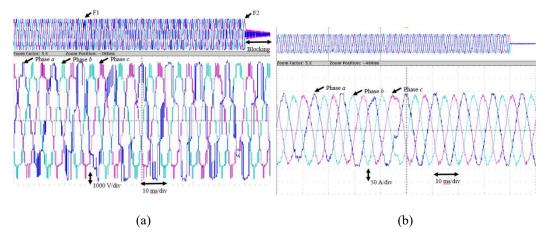

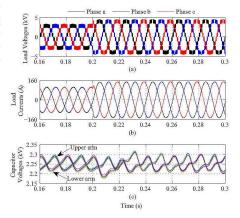

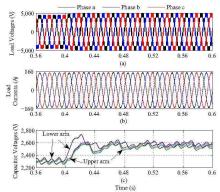

| Figure 4.13: Load waveforms of Case 1, while disabling the proposed estimation unit: a) three-phase voltages, b) three-phase load currents, c) voltages of Leg <i>a</i> submodules                                                                                       |

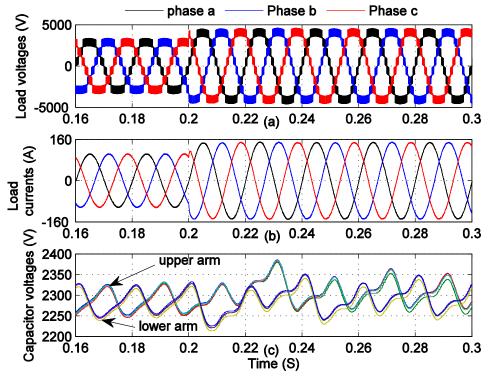

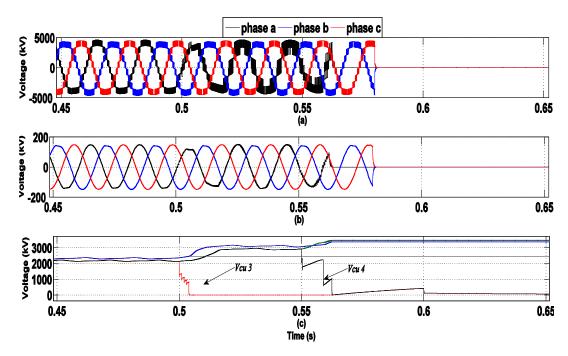

| Figure 4.14: Load waveforms of Case 1, while enabling the proposed estimation unit: a) three-phase voltages, b) three-phase load currents, c) voltages of Leg <i>a</i> submodules                                                                                        |

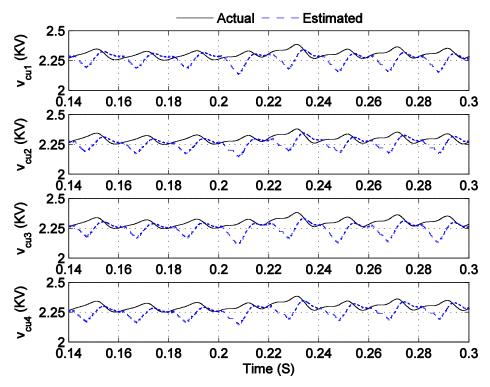

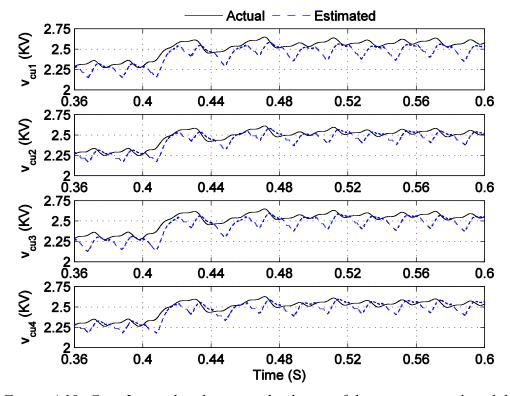

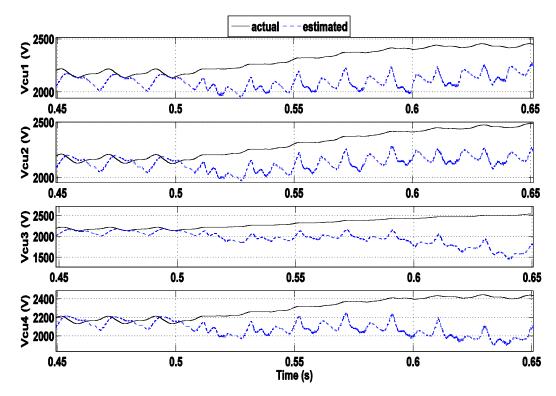

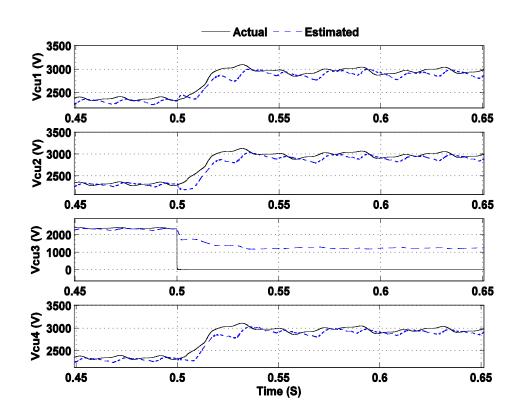

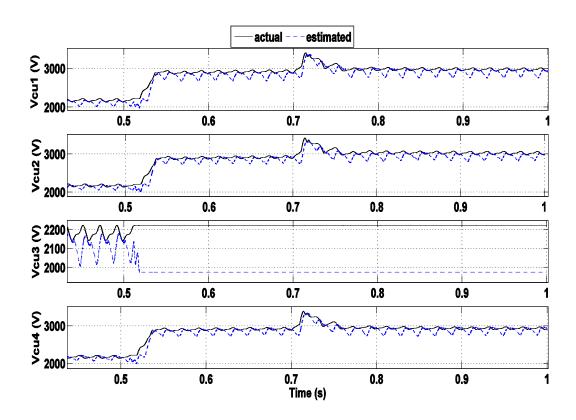

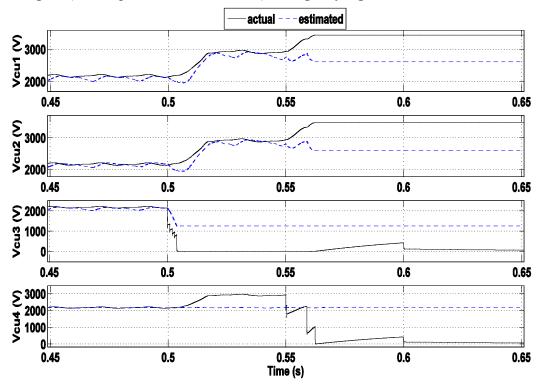

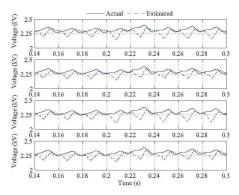

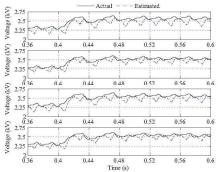

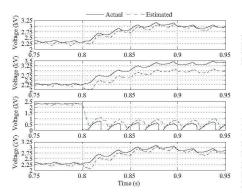

| Figure 4.15: Case 1 actual and estimated voltages of the upper arm submodules of Phase <i>a</i>                                                                                                                                                                          |

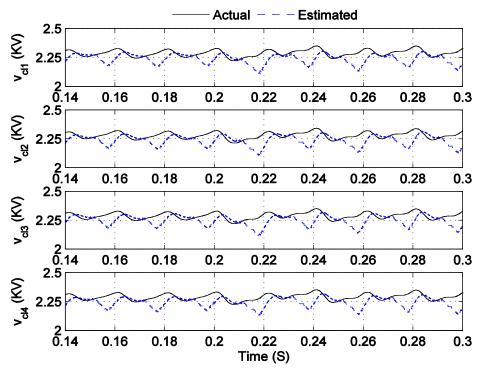

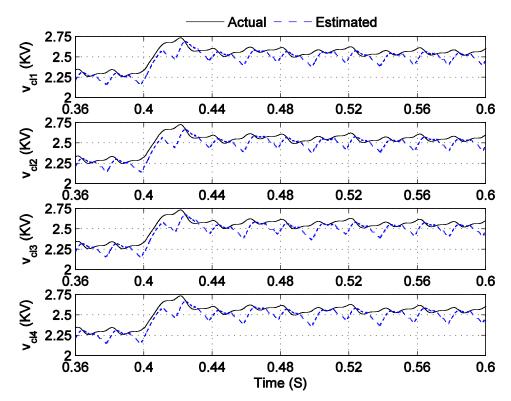

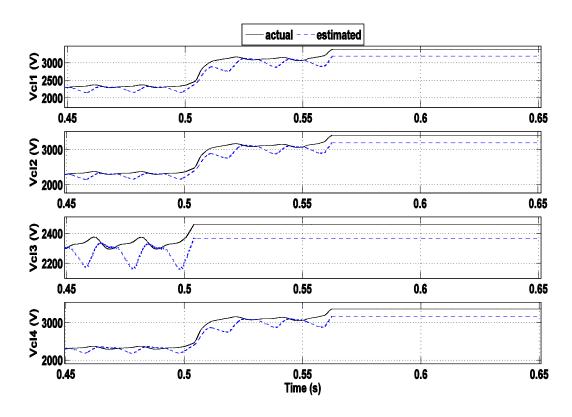

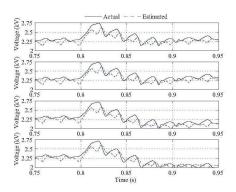

| Figure 4.16: Case 1 actual and estimated voltages of the lower arm submodules of Phase <i>a</i>                                                                                                                                                                          |

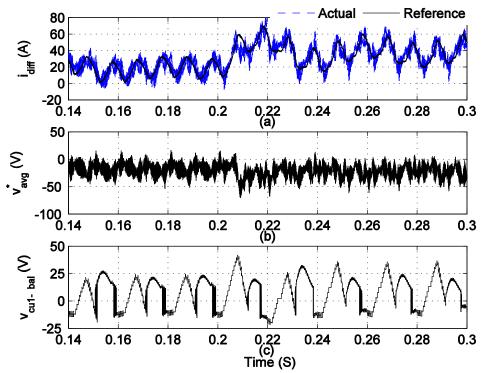

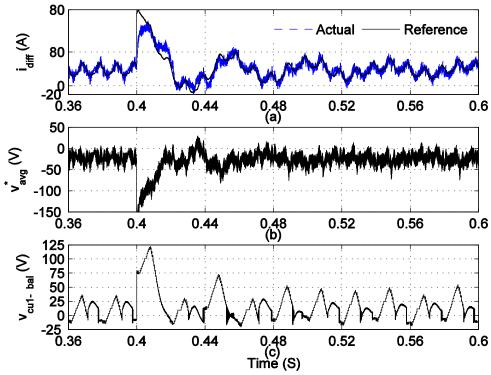

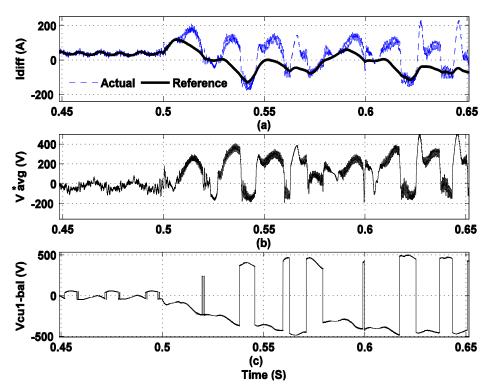

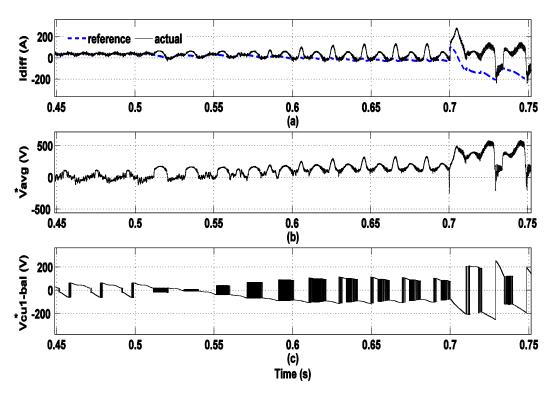

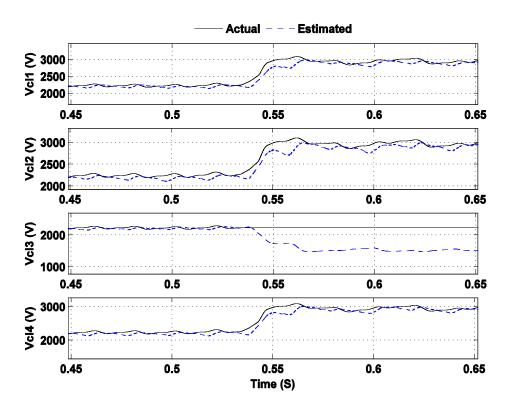

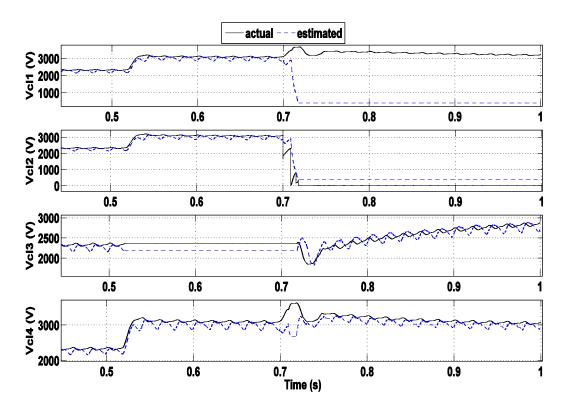

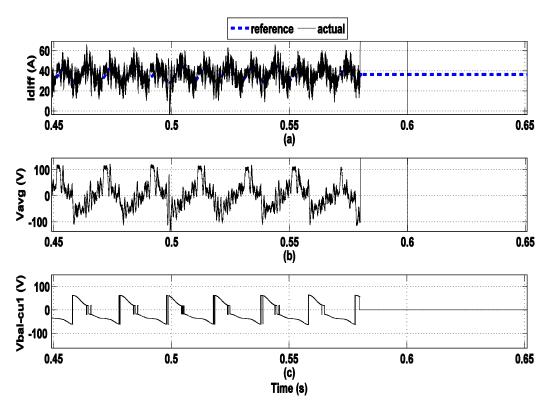

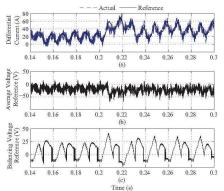

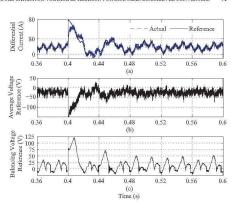

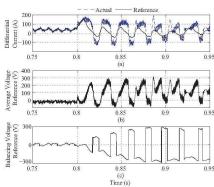

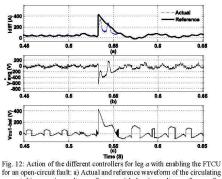

| Figure 4.17: Action of the different controllers for Leg a during Case 1: a) actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm71                         |

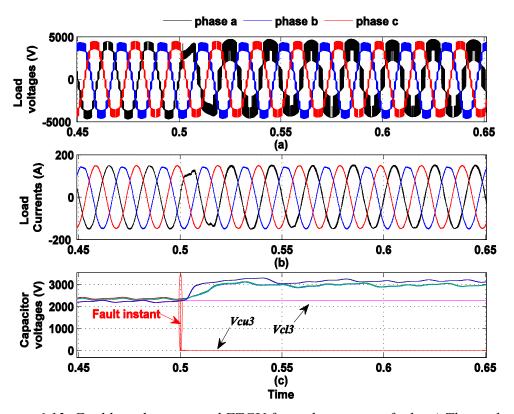

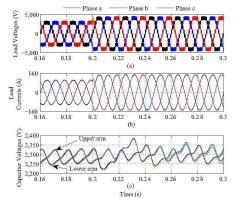

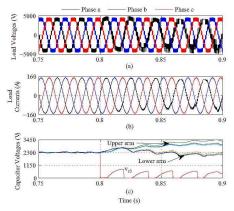

| Figure 4.18: Load waveforms of Case 2: a) three-phase voltages, b) three-phase load currents, c) voltages of Leg <i>a</i> submodules                                                                                                                                     |

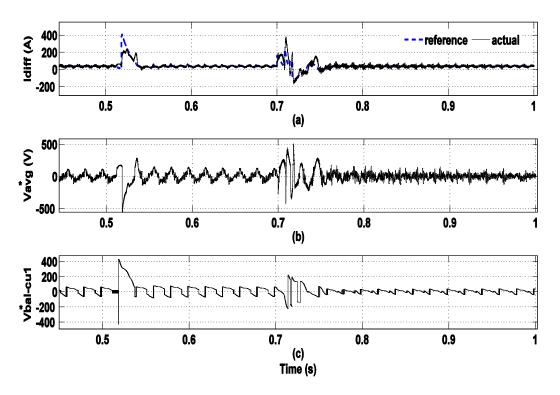

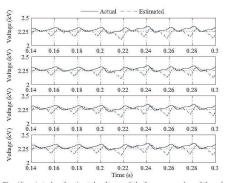

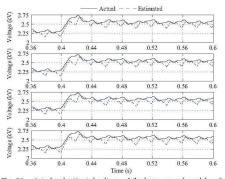

| Figure 4.19: Case 2 actual and estimated voltages of the upper arm submodules of Phase <i>a</i> during the boosting operation                                                                                                                                            |

| Figure 4.20: Case 2 actual and estimated voltages of the lower arm submodules of Phase <i>a</i> during the boosting operation                                                                                                                                            |

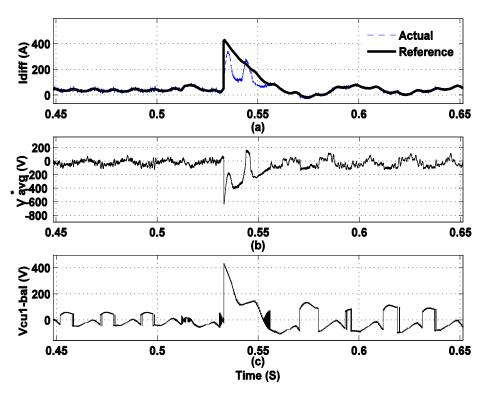

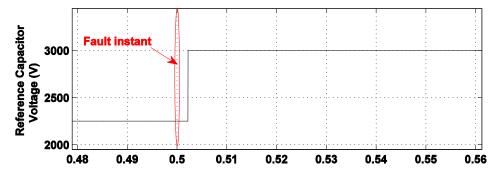

| Figure 4.21: Action of the different controllers for Leg a during the boosting operation (Case 2): a) actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

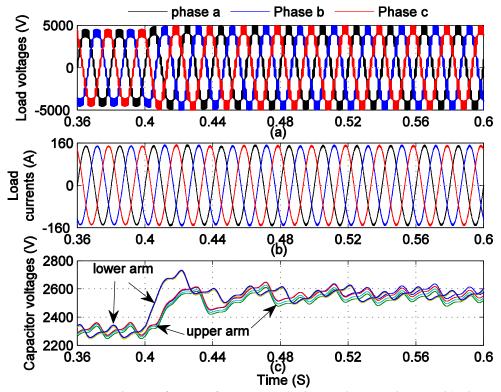

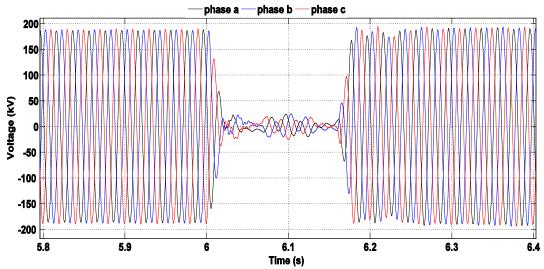

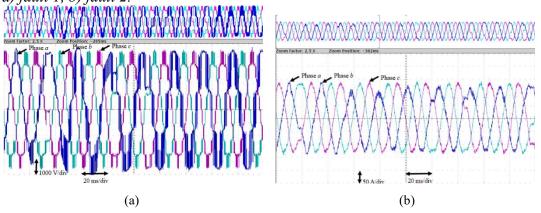

| Figure 4.22: Case 3 voltages and currents of grid: a) three-phase voltages, b) three-phase currents                                                                                                                                                                                                                   |

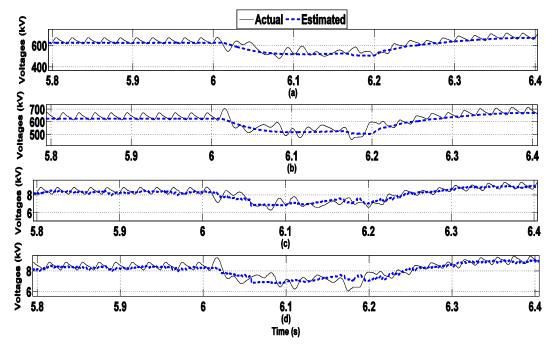

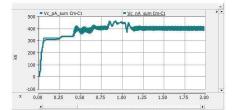

| Figure 4.23: Case 3 actual and estimated signals of submodule capacitor voltages in Leg a: a) summation of capacitor voltages in the upper arm, b) summation of capacitor voltages in the lower arm, c) capacitor voltage of one submodule in the upper arm, d) capacitor voltage of one submodule in the lower arm75 |

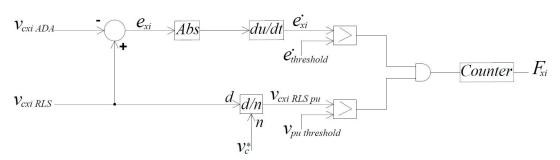

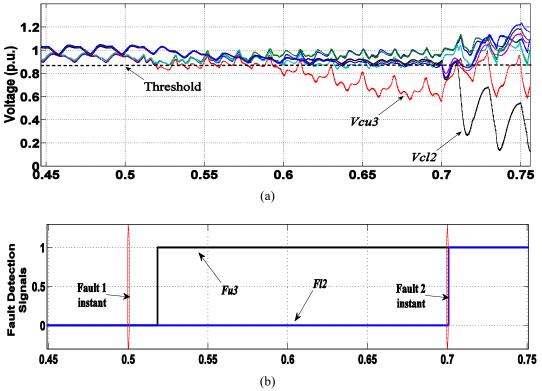

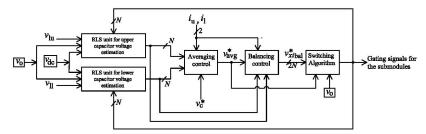

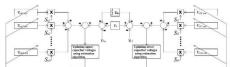

| Figure 5.1. Block diagram of the proposed FDU                                                                                                                                                                                                                                                                         |

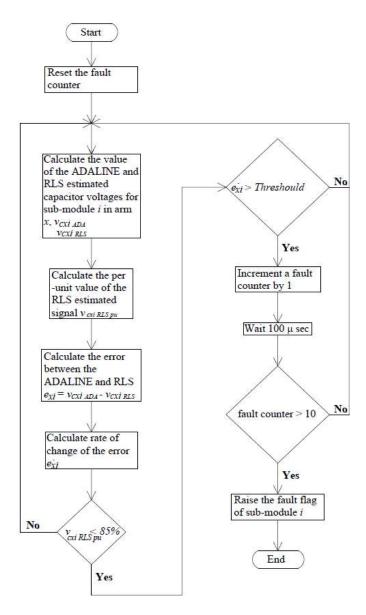

| Figure 5.2. Flowchart of the proposed fault detection technique79                                                                                                                                                                                                                                                     |

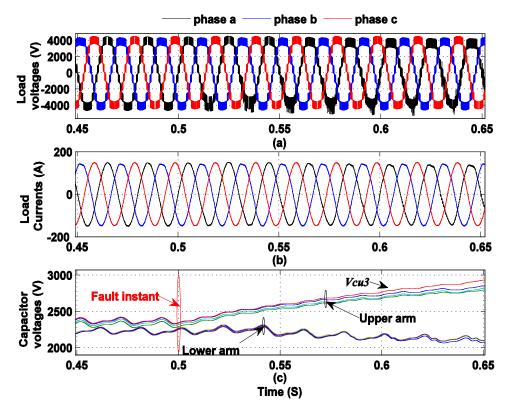

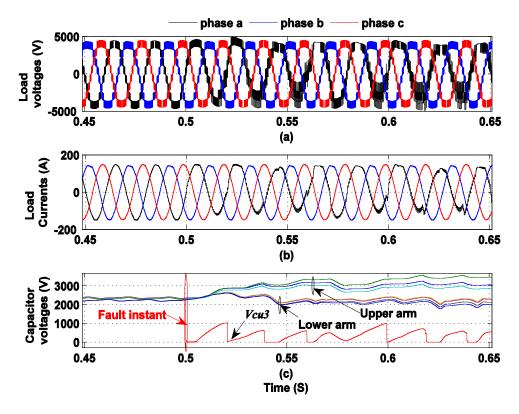

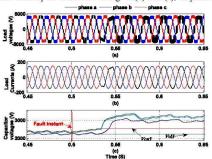

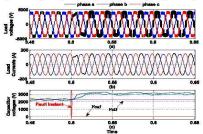

| Figure 5.3. FDU performance during an open-circuit fault on the third submodule of the upper arm: a) Three-phase voltages, b) three-phase load currents, c) voltages of leg <i>a</i> submodules                                                                                                                       |

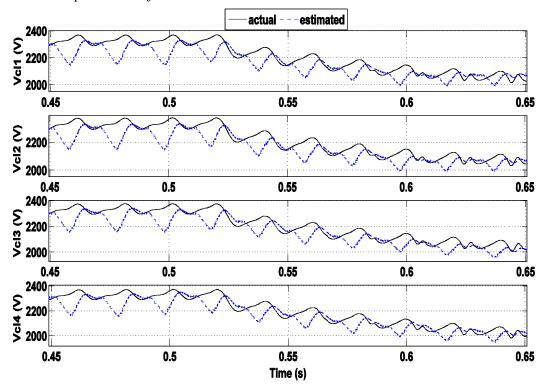

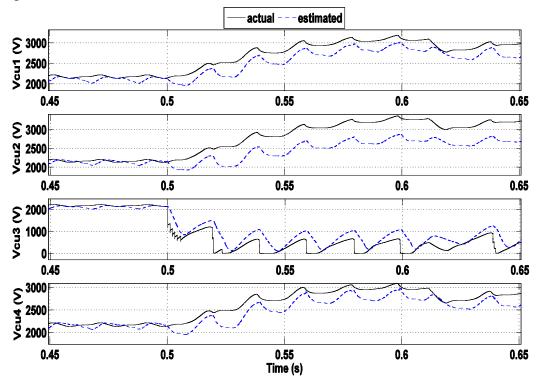

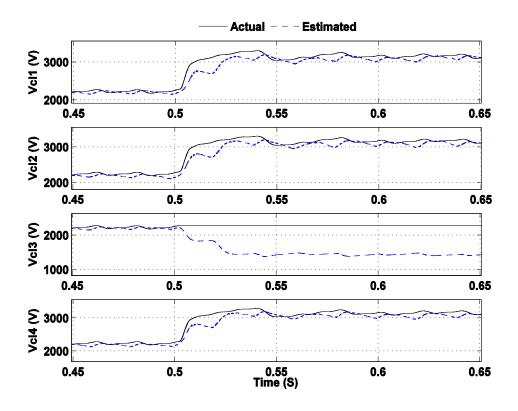

| Figure 5.4. Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under an open-circuit fault                                                                                                                                                                                                 |

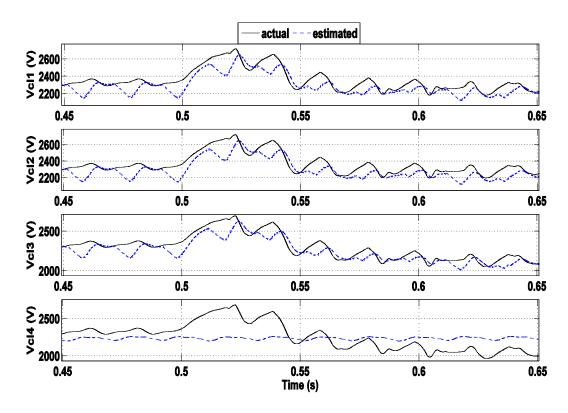

| Figure 5.5. Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under an open-circuit fault.                                                                                                                                                                                                |

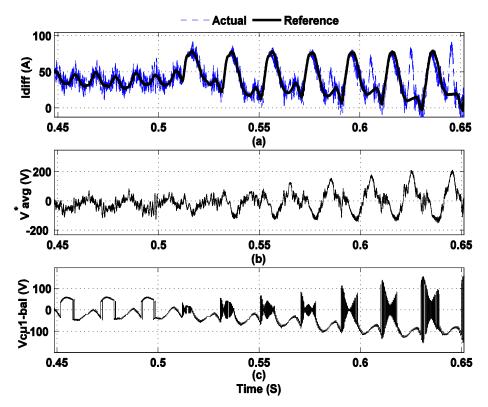

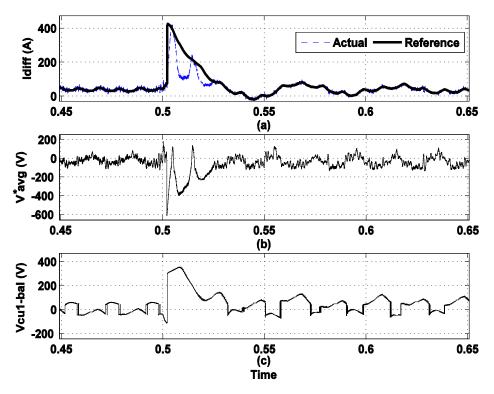

| Figure 5.6. Action of the different controllers for leg <i>a</i> during the open-circuit fault: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm                                                  |

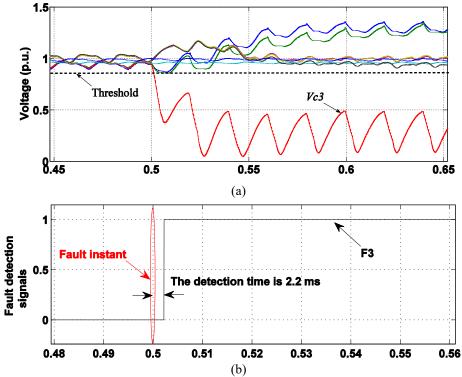

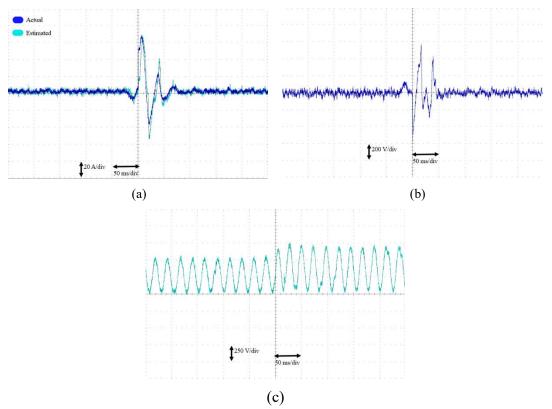

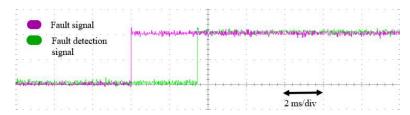

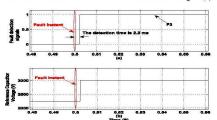

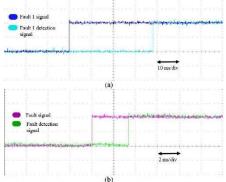

| Figure 5.7: The performance of the FDU under IGBT open circuit fault: a) The RLS estimated voltages of the upper arm of phase <i>a</i> , b) The detection time consumed by the FDU to detect the open circuit fault85                                                                                                 |

| Figure 5.8: Operation during a short-circuit fault on the third submodule of the upper arm: a) Three-phase voltages, b) three- phase load currents, c) voltages of leg <i>a</i> submodules                                                                                                                            |

| Figure 5.9: Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under a short-circuit fault                                                                                                                                                                                                 |

| Figure 5.10: Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under a short-circuit fault.                                                                                                                                                                                               |

| Figure 5.11: Action of the different controllers for leg <i>a</i> during the short-circuit fault: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm                                                |

| Figure 5.12: The performance of the FDU under IGBT short circuit fault: a) The RLS estimated voltages of the upper arm of phase a, b) The detection time consumed by the FDU to detect the open circuit fault                                                                                                         |

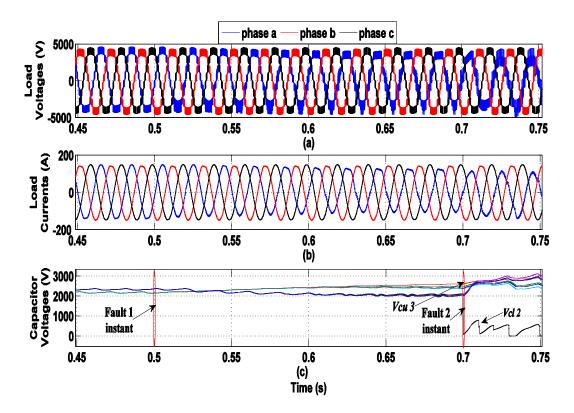

| Figure 5.13: Operation during multiple faults: a) Three-phase voltages, b) three-phase load currents, c) voltages of leg <i>a</i> submodules90                                                                                                                                                                        |

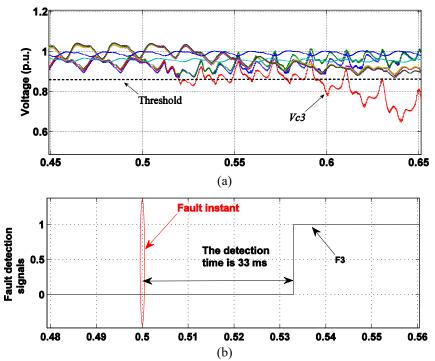

| Figure 5.14: Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under two faults                                                                                                                                                                                                           |

| Figure 5.15: Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under two faults92                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.16: Action of the different controllers for leg a during multiple faults: a) actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm                            |

| Figure 5.17: The performance of the FDU under two faults: a) The RLS estimated voltages of the upper arm of phase <i>a</i> , b) The detection time consumed by the FDU to detect the open circuit fault                                                                            |

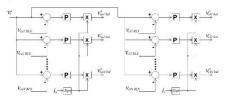

| Figure 6.1: The proposed fault tolerant control algorithm96                                                                                                                                                                                                                        |

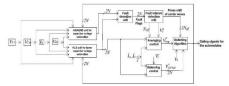

| Figure 6.2: Block diagram of the proposed MMC control strategy97                                                                                                                                                                                                                   |

| Figure 6.3: Markov chain for a modular multilevel converter without fault tolerant control                                                                                                                                                                                         |

| Figure 6.4: Markov chain of the MMC with the classical redundancy based fault tolerant control                                                                                                                                                                                     |

| Figure 6.5: Markov chain for a five-level modular multilevel converter with the proposed fault tolerant control                                                                                                                                                                    |

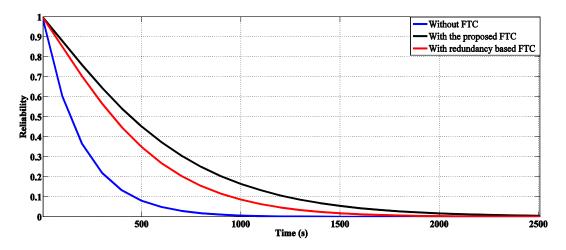

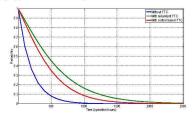

| Figure 6.6: Plot of reliability density functions before and after the application of the proposed fault tolerant control.                                                                                                                                                         |

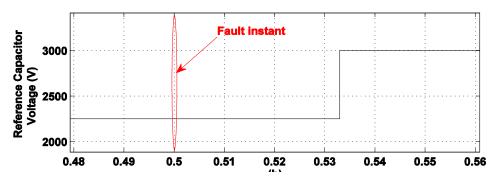

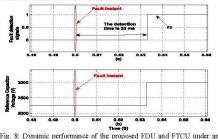

| Figure 6.7: Dynamic performance of the proposed FTCU under an open-circuit fault in a submodule                                                                                                                                                                                    |

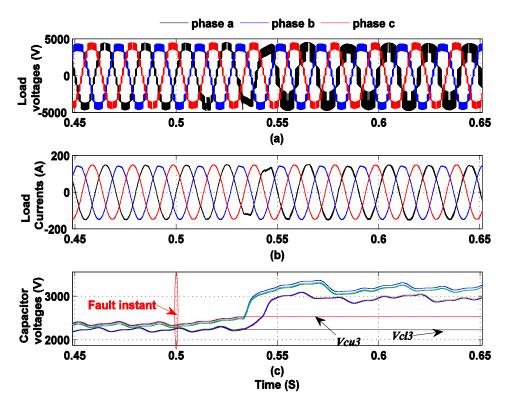

| Figure 6.8: Enabling the proposed FTCU for an open-circuit fault: a) Three-phase voltages, b) three-phase load currents, c) voltages of leg <i>a</i> submodules                                                                                                                    |

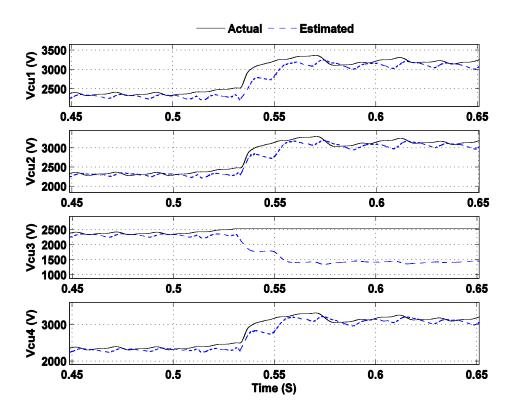

| Figure 6.9: Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under an open-circuit fault while enabling the proposed FTCU105                                                                                                                          |

| Figure 6.10: Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under an open-circuit fault while enabling the proposed FTCU105                                                                                                                         |

| Figure 6.11: Action of the different controllers for leg a with enabling the FTCU for an open-circuit fault: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm. |

| Figure 6.12: Dynamic performance of the proposed FTCU under a short-circuit fault in a submodule                                                                                                                                                                                   |

| Figure 6.13: Enabling the proposed FTCU for a short-circuit fault: a) Three-phase voltages, b) three-phase load currents, c) voltages of leg <i>a</i> submodules                                                                                                                   |

| Figure 6.14: Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under a short-circuit fault.                                                                                                                                                            |

| Figure 6.15: Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under a short-circuit fault                                                                                                                                                             |

| Figure 6.16: Action of the different controllers for leg a with enabling the FTCU for a short-circuit fault: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm  |

| Figure 6.17: Enabling the proposed FTCU for multiple faults: a) Three-phase voltages, b) three-phase load currents, c) voltages of leg <i>a</i> submodules110                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

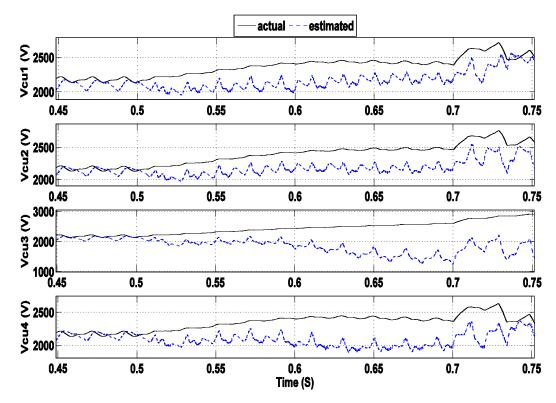

| Figure 6.18: Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under multiple faults                                                                                                                                                                      |

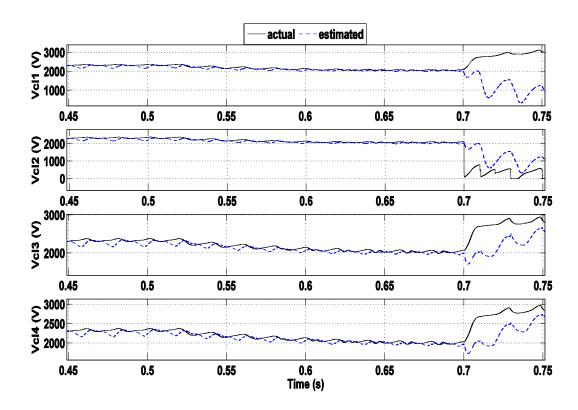

| Figure 6.19: Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under multiple faults                                                                                                                                                                      |

| Figure 6.20: Action of the different controllers for leg a with enabling the FTCU for multiple faults: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm.          |

| Figure 6.21: Dynamic performance of the proposed FTCU under cascading failure                                                                                                                                                                                                         |

| Figure 6.22: Enabling the proposed FTCU for cascading failures: a) Three-phase voltages, b) three-phase load currents, c) voltages of leg <i>a</i> submodules                                                                                                                         |

| Figure 6.23: Actual and estimated voltages of the upper arm submodules of phase <i>a</i> , under cascading failures.                                                                                                                                                                  |

| Figure 6.24: Actual and estimated voltages of the lower arm submodules of phase <i>a</i> , under cascading failures                                                                                                                                                                   |

| Figure 6.25: Action of the different controllers for leg <i>a</i> with enabling the FTCU for cascading failures: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) balancing voltage reference for the first submodule of the upper arm |

| Eigene 7.1. Charatage of the IIII aletforms                                                                                                                                                                                                                                           |

| Figure 7.1: Structure of the HIL platform                                                                                                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL                                                                                                                                                                                                       |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

| Figure 7.2: The HIL platform system components: a) the block diagram of the HIL platform, b) a snapshot of the HIL system                                                                                                                                                             |

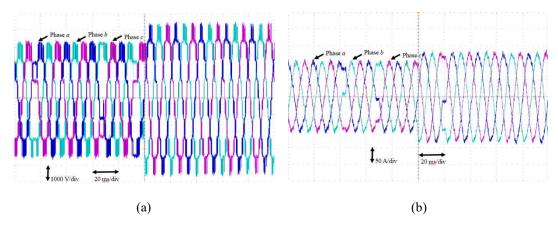

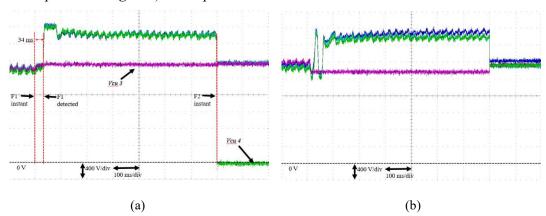

| Figure 7.13: Performance of the proposed control for an open-circuit fault: a) Three-phase voltages, b) three-phase load currents                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.14: Performance of the proposed control for an open-circuit fault: a) submodule voltages of upper arm in leg a, b) submodule voltages of lower arm in leg a                                                                                                                           |

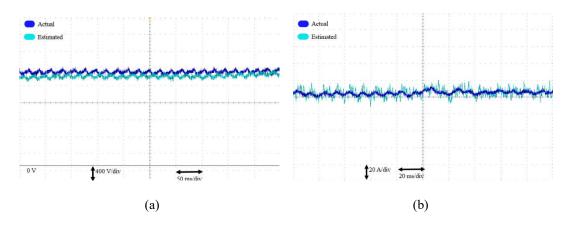

| Figure 7.15: RLS-estimated signals in the upper arm of leg <i>a</i> under open-circuit fault: a) first submodule (healthy), b) third submodule (faulty)                                                                                                                                        |

| Figure 7.16: Action of the different controllers for leg a with enabling the proposed control for an open-circuit fault: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) modulating voltage reference for the first submodule of the upper arm |

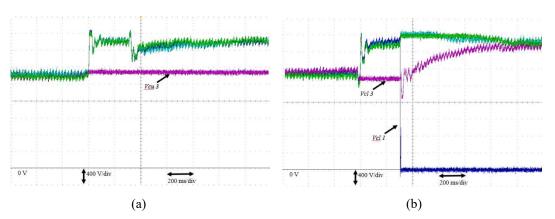

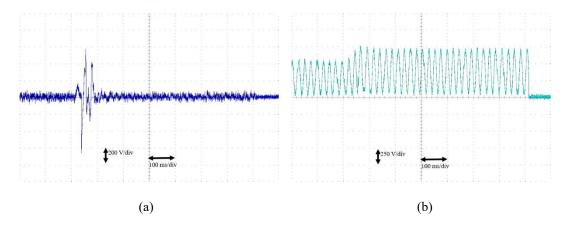

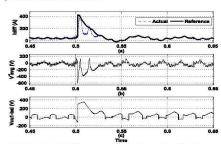

| Figure 7.17: Dynamic performance of the proposed control under a short-circuit fault in a submodule.                                                                                                                                                                                           |

| Figure 7.18: Enabling the proposed control for a short-circuit fault: a) Three-phase voltages, b) three-phase load currents                                                                                                                                                                    |

| Figure 7.19: Enabling the proposed control for a short-circuit fault: a) submodule voltages of upper arm in $\log a$ , b) submodule voltages of lower arm in $\log a$ 130                                                                                                                      |

| Figure 7.20. RLS-estimated signals in the upper arm of leg <i>a</i> under short circuit: a) first submodule (healthy), b) third submodule (faulty)                                                                                                                                             |

| Figure 7.21: Action of the different controllers for leg a with enabling the proposed control for a short-circuit fault: a) Actual and reference waveform of the circulating current, b) averaging voltage reference, c) modulating voltage reference for the first submodule of the upper arm |

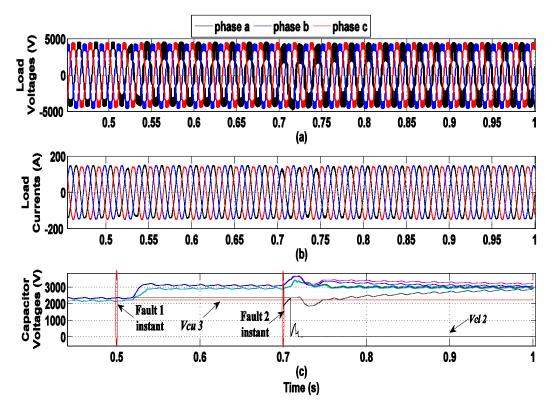

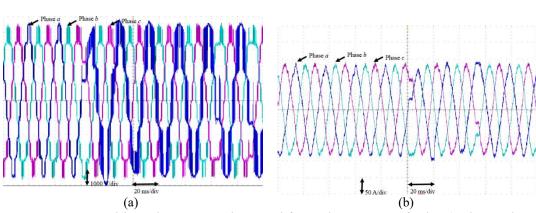

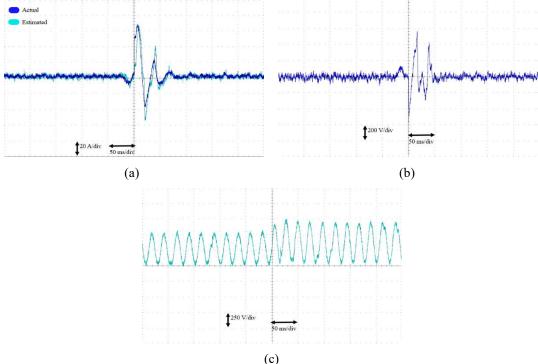

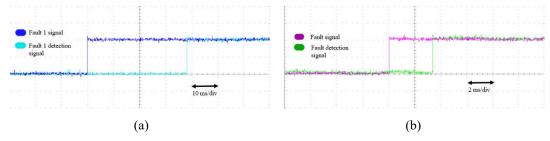

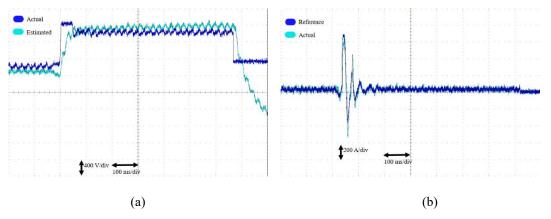

| Figure 7.22: Dynamic performance of the proposed control under multiple faults: a) fault 1, b) fault 2                                                                                                                                                                                         |

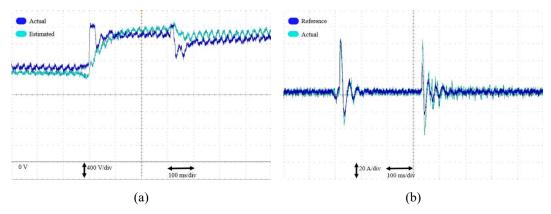

| Figure 7.24: The performance of the proposed control under multiple faults: a) submodule voltages of upper arm in leg a, b) submodule voltages of lower arm in leg a                                                                                                                           |

| Figure 7.25: Action of the different controllers for leg <i>a</i> with enabling the proposed control for multiple failure: a) The capacitor voltage estimation of submodule <i>Vcu1</i> , b) actual and reference waveform of the circulating current                                          |

| Figure 7.26: Action of the different controllers for leg a with enabling the proposed control for multiple failure: a) averaging voltage reference, b) modulating voltage reference for the first submodule of the upper arm                                                                   |

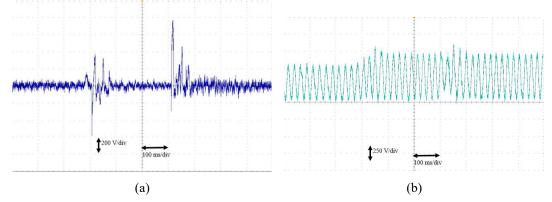

| Figure 7.27: The performance of the proposed strategy under cascading failure: a) three-phase voltages, b) three-phase load currents                                                                                                                                                           |

| Figure 7.28: The performance of the proposed strategy under cascading failure: a) capacitor voltages of the upper arm in phase <i>a</i> , b) capacitor voltages of the lower arm in phase <i>a</i>                                                                                             |

| Figure 7.29: Action of the different controllers for leg a: a) The capacitor voltage estimation of SM <i>Vcu1</i> , b) Actual and reference waveforms of the circulating current                                                                                                               |

| Figure 7.30: Action of the different controllers for leg a: a) averaging voltage reference, b) Modulation signal for the first SM of the upper arm                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure A.1: Active and reactive power control                                                                                                                        |

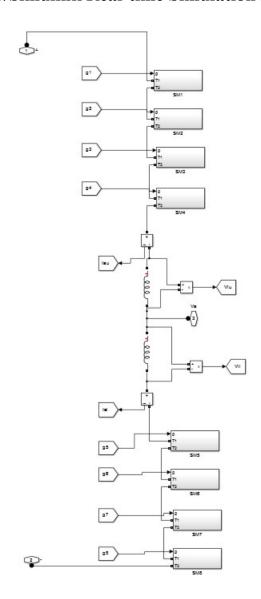

| Figure B.1: The simulated 5 level MMC                                                                                                                                |

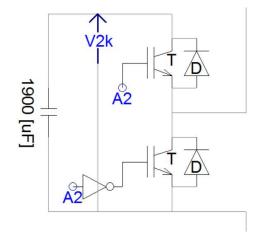

| Figure B.2: The submodule model                                                                                                                                      |

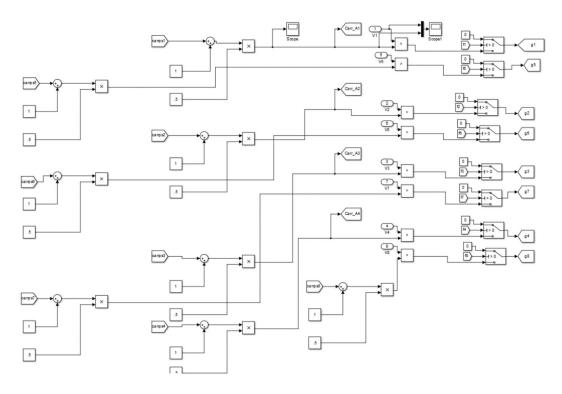

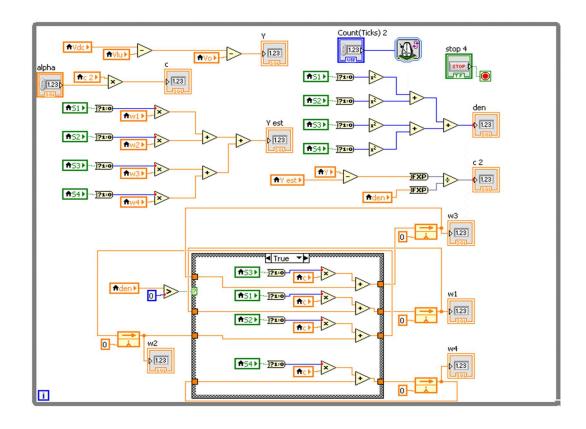

| Figure B.3: The RLS programming block                                                                                                                                |

| Figure B.4: The ADALINE programming block                                                                                                                            |

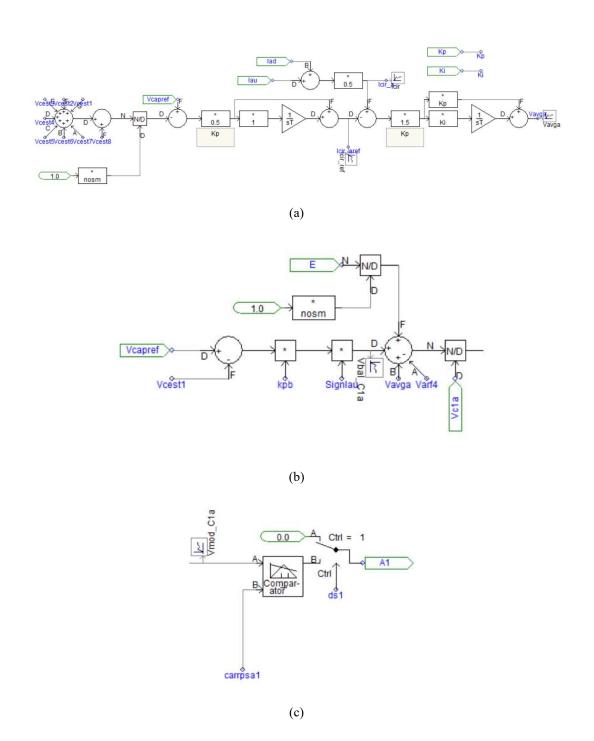

| Figure B.5: The block of the proposed capacitor voltage algorithm: a) The averaging controller, b) The balancing controller, c) The PS-PWM modulation technique. 162 |

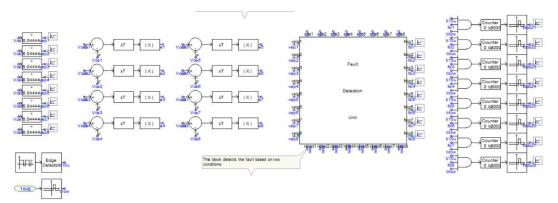

| Figure B.6: The block of the proposed FDU                                                                                                                            |

| Figure B.7: The block of the proposed FDU                                                                                                                            |

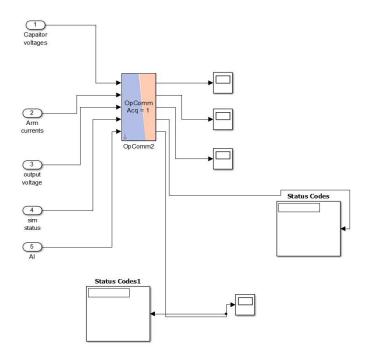

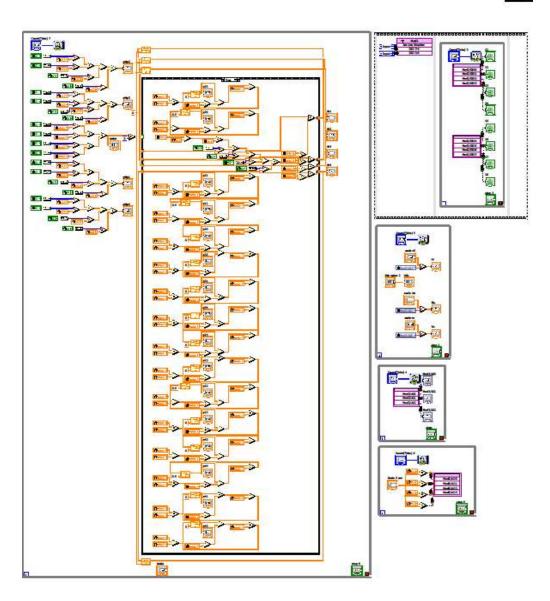

| Figure C.1: The block of the proposed FDU for one leg                                                                                                                |

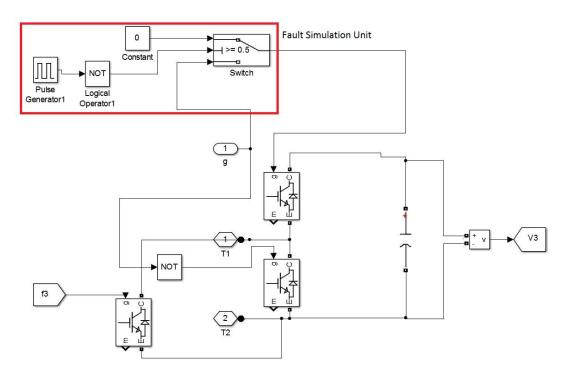

| Figure C.2: The block of submodule including the fault simulation unit172                                                                                            |

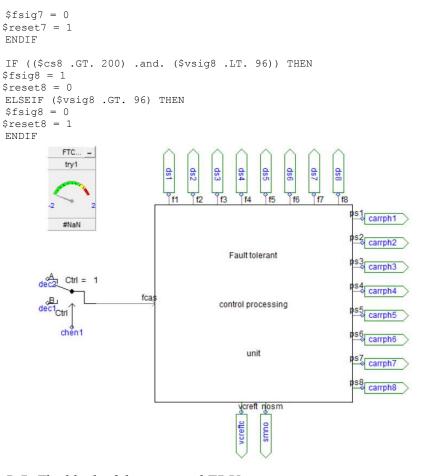

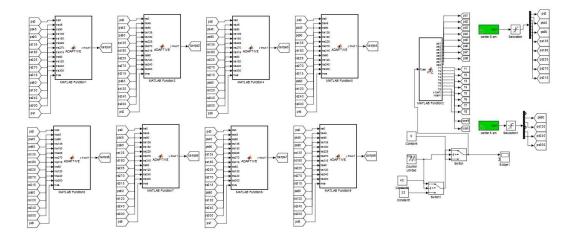

| Figure C.3: The blocks of the proposed FTCU                                                                                                                          |

| Figure C.4: The blocks of the PS-PWM switching algorithm                                                                                                             |

| Figure C.5: The Monitoring console                                                                                                                                   |

| Figure C.6: The LABVIEW block of the ADALINE capacitor voltage estimation algorithm for one arm                                                                      |

| Figure C.7: The LABVIEW block of the RLS capacitor voltage estimation algorithm for one arm                                                                          |

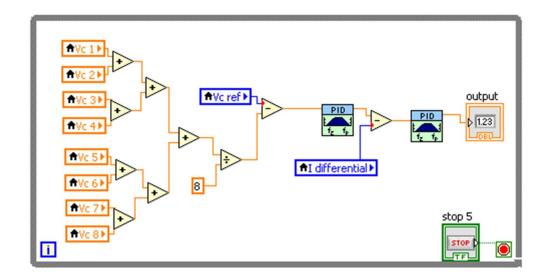

| Figure C.8: The LABVIEW block of the averaging control for one leg181                                                                                                |

| Figure C.9: The LABVIEW block of the balancing control for one submodule181                                                                                          |

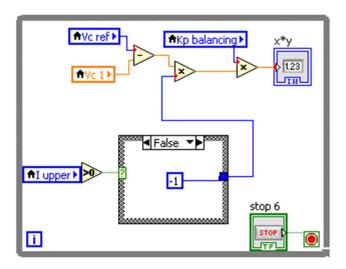

| Figure C.10: The LABVIEW block of the proposed FDU (for one submodule)                                                                                               |

| Figure C.11: The LABVIEW graphical user interface of the capacitor voltage estimation                                                                                |

| Figure C.12: The LABVIEW graphical user interface of the capacitor voltage balancing control                                                                         |

| Figure C.13: The LABVIEW graphical user interface of the proposed FDU183                                                                                             |

### **List of Tables**

| Table 2.1: Comparison between different switching algorithms used for MMCs24                          |

|-------------------------------------------------------------------------------------------------------|

| Table 3.1: Faults in submodule IGBTs                                                                  |

| Table 3.2: Relationship between submodule output voltage and arm currents during open circuit faults  |

| Table 3.3: Relationship between submodule output voltage and arm currents during short circuit faults |

| Table 3.4: Faults in submodule capacitors                                                             |

| Table 3.5: Comparison between common MMC fault detection techniques proposed in literature            |

| Table 4.1: Summary of the MMC parameters of the first model64                                         |

| Table 4.2: Summary of the MMC parameters of the second model67                                        |

#### **List of Abbreviations**

ADALINE Adaptive linear neuron.

ANN Artificial neural network.

CSC Current source converter.

DFIG Doubly fed induction gene

DFIG Doubly fed induction generator. ESR Equivalent series resistance.

FACTS Flexible alternating current transmission systems.

FDU Fault detection unit.

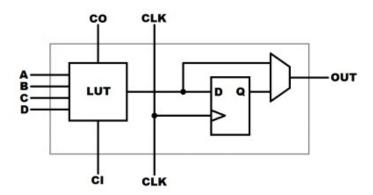

FPGA Field programmable gate array.

FTC Fault tolerant control.

FCU Fault tolerant control unit.

HIL Hardware in the loop.

HVAC High voltage AC.

HVDC High voltage direct current.

IGBT Insulated gate bipolar transistor.

LCC Line commutated converter.

LS-PWM Level shifted pulse-width modulation.

LUT Look-up table.

MMC Modular multilevel converter.

MTTF Mean time to failure.

NLM Nearest level modulation.

PID Proportional integral derivative.

PMSG permanent magnet synchronous generator. PS-PWM Phase shifted pulse-width modulation.

PWM Pulse-width modulation.

RLS Recursive least squares.

SMO Sliding mode observer.

SVM Space vector modulation.

THD Total harmonic distortion.

VSC Voltage source converter.

# Chapter 1

# Introduction

#### 1.1 Background

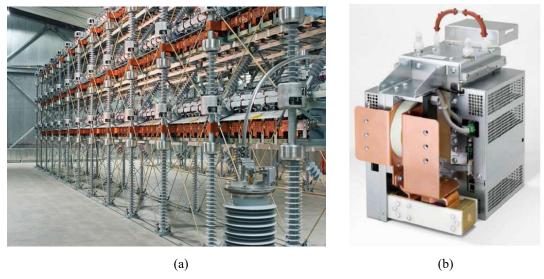

Voltage source converters (VSC) are increasingly being used in the transmission and distribution of bulk power, due to their advantages over the line commutated converters (LCC). This includes the ability to control active and reactive power independently, supply weak or passive networks, and lower the footprint [1]. Although VSCs have many topologies, the modular multilevel converter (MMC) is considered to be the most suitable converter to be used in high voltage circuits. This is due to their features, including the ability to transmit electric power over high voltage levels directly, the improved quality of output power, and the high efficiency when compared to other multilevel converters [2]. Figure 1.1, which shows a 401-level MMC made by Siemens, illustrates another special feature of MMCs, which is the compact size. This gives a unique advantage for MMCs over other converter topologies when the space allowed for construction is limited.

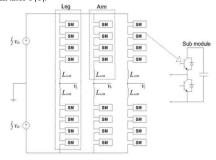

The MMC is basically formed from a series connection of submodules, which can be either half bridge or full bridge. This is the main reason for calling it modular. Increasing the number of submodules means that the number of voltage levels are increased, which is directly translated into lower harmonic content and enhances the ability to generate higher voltages.

Figure 1.1: A 401-level MMC made by Siemens [3]: a) a picture of the MMC, b) a picture for the submodule.

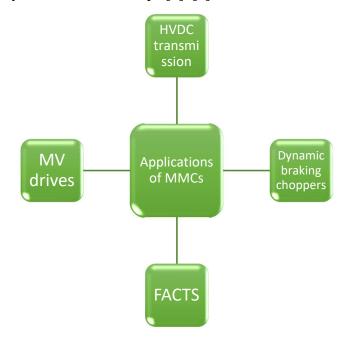

As illustrated in Figure 1.2, the applications of MMCs have covered most high and medium voltage applications that need the utilisation of power converters. The applications of the MMC include high voltage direct current (HVDC) transmission, MV drives, flexible AC transmission systems (FACTS), and dynamic braking choppers [4]. Furthermore, some research has been recently conducted to utilise the MMC in special applications, such as railway electric traction systems, in which the MMC works as a medium voltage transformer-less converter, which is used to supply the traction motors [5], [6]. In addition, the MMC can applied be in the propulsion systems of electric ships [7], [8].

Figure 1.2: Applications of MMCs.

#### 1.2 Motivation and Research Objectives

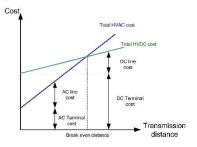

Today, DC to AC conversions are found in many applications in modern power systems, particularly in the transmission and distribution of electrical energy. Recently, DC/AC converters play an essential role in the interface of offshore wind energy with the utility grid. This is simply because the transmission along HVDC lines is much more efficient compared with the high voltage alternating current (HVAC) transmission over long distances [9].

The current source converter (CSC) was the first converter invented for this particular purpose. The CSC is formed from six thyristors connected in the form of a three-phase bridge connected to the DC supply. Although the CSC is considered very old technology, it is still used in the connection of the renewable energies to the grid in various modern projects [10]. This is simply because of the many advantages, such as the ability to convert high amounts of power, the low manufacturing price, and the high reliability [11]. However, it has some disadvantages and limitations that make it unsuitable for some applications [12], [13]. The main disadvantages are the necessity to have filtering components because of the low order harmonics, the impossibility of changing the current direction, and the inability to independently control reactive power. These limitations have motivated the researchers to invent VSC [13].

The two-level VSC has a simple configuration, which is similar to the CSC but with IGBT instead of the thyristors. This construction has changed the philosophy of switching since the IGBT is fully controllable during turning on and off. On some occasions, the switching device is formed from series-connected IGBTs to withstand high voltage stress [14]. One of the important advantages of the VSC is its ability to control active and reactive powers independently. Moreover, it can supply weak and passive networks. It also has a relatively low footprint compared to the CSC [15]. Despite having all of these advantages, the two-level VSC suffers from some drawbacks that can make it unsuitable for the application of grid interconnection. For example, having series-connected IGBTs increases the switching losses and makes it difficult to predict the transient response of the

switching device. It also is necessary to incorporate DC-link capacitors, which are very big and have a short life expectancy [16]. Moreover, the two-level VSC has no immunity against DC faults, as it fails to support the AC grid with active power [17]. Adding to these drawbacks, the two-level VSCs cannot exchange electricity over high voltage levels directly without using step-up transformers [18].

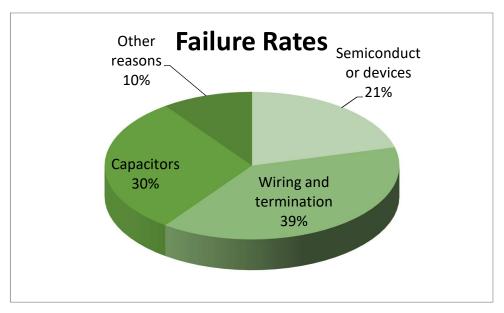

Due to the problems associated with LCC and VSC, researchers have been directed to multilevel converters (particularly MMCs). The modularity of the MMC offers a generous advantage, which is the ability to generate high voltage levels using a sufficient number of submodules. Although having a series connection of submodules with floating capacitor voltages brings the advantages of a staircase output waveform with low switching frequencies, it increases the level of complexity of the system from the control point of view, as all submodules must be charged to the same voltage level to assure the accurate and stable operation of the converter [19]. Moreover, in order to maintain the output voltage level of the converter, the capacitor voltages must be kept at a reference value [20], [21]. The process of keeping the capacitor voltages within a pre-defined reference is called capacitor voltage balancing control, which is achieved by a dedicated controller called the MMC inner controller [21]. The MMC inner controller should perform some tasks in parallel with the balancing of the voltages across the submodule capacitors. One of the important tasks is protecting the MMC from internal submodule faults, such as power electronic device faults and submodule capacitor faults. As demonstrated in Figure 1.3, which shows the general probability of occurrence for these faults in power converters, power semiconductor devices and capacitors have the highest probability of fault in the MMC with a percentage of 51% [22], [23]. Since the MMC normally works in critical applications, which always require high levels of reliability and supply security, its inner control system should be able to operate with a sustained fault (e.g., insulated gate bipolar transistors (IGBT) failure) until the next maintenance event [24], which means that the inner control system should have fault tolerant control (FTC) capability. This concept increases the reliability of the MMC, as it increases the availability of the converter, even in the case of having an internal fault in order to operate the converter under fail-safe operation conditions. It is important to mention that the process of FTC must be accompanied with a fault detection facility for the purpose

of maintaining safe management of MMC faults. This process not only detects the fault but also localises it to enable the FTC algorithm to isolate the faulty submodule.

Figure 1.3: Faults probabilities in power converters.

Additionally, the fault diagnosis process has a real challenge to detect the internal DC fault very quickly because, in DC systems, the DC fault current rises to its peak value in a few milliseconds [25].

The volume of the research on fault detection and FTC systems for MMCs is insignificant when compared with the huge challenges surrounding this research area. Moreover, most of the fault detection and tolerant control techniques presented in literature are considered to be expensive, as they require either redundant components or extra sensors [26].

The aim of this thesis is to develop an improved MMC inner controller, which is responsible for balancing the voltages of the submodule capacitors with integrating an ultra-fast fault diagnosis and FTC capability against submodule faults, enabling the MMC to be safely operated in normal conditions as well as abnormal conditions. Furthermore, the developed technique should not need any extra sensors, special power circuits, or even redundant components to make it competitive in cost as well as in performance.

The objectives of the thesis are the following:

- To carry out an intensive literature review in the area of capacitor voltage balancing, fault diagnosis, and tolerant control in MMC systems. This review should index the different faults that can affect the MMC submodules, showing the root cause for each fault and linking it with different techniques proposed in the past.

- To implement a new MMC inner controller, which contains the following subsystems:

- Voltage balancing of submodule capacitors without the need to measure the actual voltages so that there is no more need for capacitor voltage sensors.

- Fault diagnostic scheme, which is able to detect and localise submodule faults with effective performance in terms of accuracy and time without adding any extra sensing elements or special power circuits.

- O A FTC scheme, which controls the MMC in abnormal operating conditions when a submodule fault occurs. This scheme should achieve a fail-safe operation until the next shut down for maintenance with increased power quality without incorporating any redundant components.

- To test the developed fault diagnosis and tolerant control techniques

on the MMC model to study the effectiveness of these methods by

means of PSCAD simulation tool and hardware in the loop (HIL)

testing techniques, incorporating a physical controller and a real-time

digital simulator to prove the effectiveness of the proposed

techniques physically as well as theoretically.

#### 1.3 Thesis Outline

Chapter 2 investigates the structure, theory of operation, mathematical representation, and modulation of MMCs. Furthermore, the design considerations that should be met while selecting the ratings of MMC components are also investigated.

Chapter 3 presents a literature review over the main topics covered in the thesis. First, common capacitor voltage balancing techniques are investigated to characterise the advantages and disadvantages of each technique, aiming to determine the real problems associated with the process of capacitor voltage balancing. Then, the MMC submodule faults are mapped with the root cause and consequences associated with each fault. Finally, popular fault diagnosis and tolerant control strategies that are proposed in literature are also discussed.

In Chapter 4, a new capacitor voltage balancing strategy based on capacitor voltage estimation techniques is presented. Two capacitor voltage estimation techniques based on the adaptive linear neuron (ADALINE) and recursive least square (RLS) algorithms are introduced, and a comparison between the two techniques is also conducted to select the most suitable one to be incorporated into the proposed capacitor voltage balancing technique. Moreover, two simulation models are introduced for the purpose of testing the proposed capacitor voltage balancing techniques under several operation conditions.

Chapter 5 introduces a new fault detection technique based on capacitor voltage estimation algorithms, which is able to detect faults associated with MMC submodules. In addition, the chapter shows some simulation results that show the behaviour and performance of the proposed technique under different faulty conditions.

Chapter 6 presents the proposed FTC technique, which is based on a special sorting algorithm. Moreover, the reliability of the MMC is studied before and after the application of the proposed technique to assess the amount of reliability enhancement. Finally, simulation results of the entire control system are discussed.

Chapter 7 shows the validation of the proposed methods mentioned in Chapters 4, 5, and 6 by means of HIL of simulation through connecting a real-time digital simulator to a real-time controller. It also presents the practical assessment of the proposed MMC inner control when applied in a real application. The assessment mainly focuses on the amount of computational burden of the proposed techniques.

Chapter 8 shows the conclusion of the thesis, focusing on the main contributions to the knowledge. Furthermore, it also presents some recommendations for future research.

#### 1.4 List of Publications

#### 1.4.1 Journal publications

- M. Abdelsalam, M. Marei, S. Tennakoon, and A. Griffiths, 'Capacitor voltage balancing strategy based on submodule capacitor voltage estimation for modular multilevel converters'. *CSEE Journal of Power and Energy Systems*, 2(1), pp. 65-73, 2016.

- M. Abdelsalam, M. Marei, and S. Tennakoon, 'An Integrated Control Strategy with Fault Detection and Tolerant Control Capability Based on Capacitor Voltage Estimation for Modular Multi-level'. *IEEE Transactions* on *Industry Applications*, Early access.

- M. Abdelsalam, M. Marei, S. Tennakoon and H. Diab 'A Fault Tolerant Based Control Strategy for Modular Multi-Level Converters'. *PLOS ONE Journal*. – Under review.

- M. Abdelsalam, M. Marei, and S. Tennakoon, 'A Centralized Control Strategy for Hybrid Modular Multi-Level Converters with Fault Detection and Tolerant Control Capabilities', *Journal of Power Electronics* – Under review.

#### 1.4.2 Conference publications

- M. Abdelsalam, S. Tennakoon, A. L. Griffiths, and M. Marei, 'Investigation of submodule fault types of modular multi-level converters in HVDC networks'. 50th International Universities Power Engineering Conference (UPEC), (pp. 1-6), IEEE, 2015.

- M. Abdelsalam, S. Tennakoon, A. L. Griffiths, and M. Marei, 'Fault detection, diagnosis and tolerant control of MMCs for HVDC Networks'. The 5th IET International Conference on Renewable Power Generation.

- M. Abdelsalam, M. Marei, H. Diab, S. Tennakoon, and A. L. Griffiths, 'Detection and Diagnosis of Submodule Faults for Modular Multilevel

- Converters'. 51st International Universities Power Engineering Conference (UPEC).

- M. Abdelsalam, S. Tennakoon, H. Diab, and M. Marei, 'An ADALINE Based Capacitor Voltage Estimation Algorithm for MMCs', *The XIXth International Symposium on Electrical Apparatus and Technologies (SIELA 2016)*.

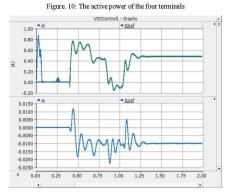

- M. Moussa, M. Abdelsalam, and H. Diab, 'Enhanced Approach for Modelling and Simulation of Modular Multilevel Converter Based Multiterminal DC Grids', UKSim-AMSS 18th International Conference on Modelling & Simulation.

#### 1.4.3 Co-authored conference publications

- H. Diab, M. Marei, M. Abdelsalam, S. Tennakoon, and C. Gould, 'Real Time Simulation of a Current Flow Controller for High Voltage DC Grids Applications', 51st International Universities Power Engineering Conference (UPEC).

- H. Diab, S. Tennakoon, M. Abdelsalam, and M. Marei, 'A Current Flow Control Apparatus for Meshed Multi-Terminal DC Grids', *The XIXth* International Symposium on Electrical Apparatus and Technologies (SIELA 2016).

# Chapter 2

# Modular Multilevel Converters: Structure, Operation, and Modulation

#### 2.1 Introduction

This chapter presents a literature review on the structure, operation, and modulation techniques of MMCs. First, a brief introduction about multilevel converters is presented. Then, an intensive investigation on the MMC is conducted focusing on its structure, principles of operation, and mathematical model. In addition, a review of the different modulation techniques used for MMCs is also conducted. Finally, the design considerations of MMCs are presented, showing the selection procedure of arm inductors and submodule capacitors.

#### 2.2 Multilevel Converters

The limitations of LCC and VSC (mentioned in Chapter 1) have directed researchers to invent multilevel converters, which are considered very promising for the application of transmission and distribution systems [27]. Unlike two-level VSCs, multilevel converters have advantages, such as the following [28]:

• The ability to transfer high power levels directly without the incorporation of interface power transformers.

- Improved efficiency due to the low switching frequency, which decreases the switching losses.

- Improved quality of output voltage due to the high number of voltage levels requiring no harmonic filters.

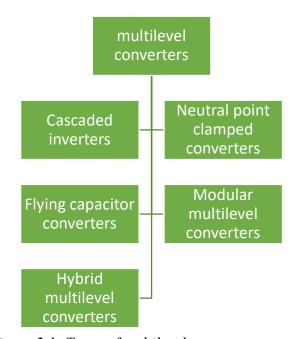

Features such as these have motivated researchers to implement a wide range of configurations for multilevel converters, as demonstrated in Figure 2.1. These are explained in the following subsections.

Figure 2.1: Types of multilevel converters.

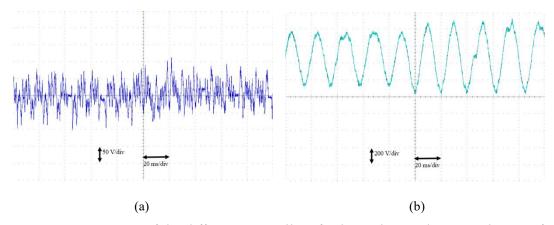

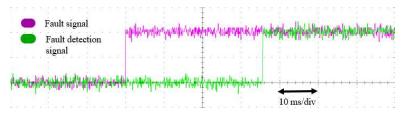

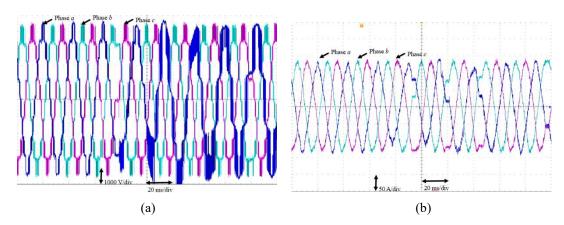

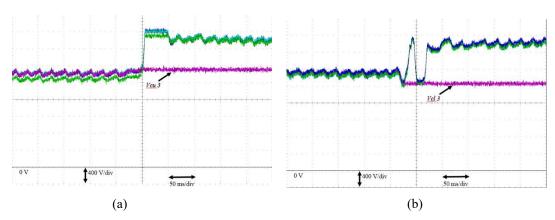

#### 2.2.1 Cascaded H-Bridge converter